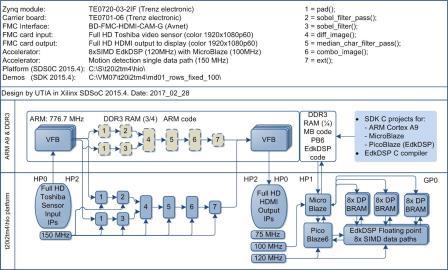

Video Processing Demonstrator with Full HD Sensor and 8xSIMD EdkDSP Accelerator IP Core

Description

This application note and evaluation package describes use of an evaluation package for the Xilinx SDK 2015.4 SW environment with these standalone, HW accelerated video processing demos designed in the Xilinx SDSoC 2015.4 environment:

- 3 edge detection video processing designs with separate HW accelerated data paths.

- These demos present the possibility to define different HW paths by different source C/C++ functions. This is important for covering of the borders lines of the parallel processed parts of the frame.

- HW accelerators can process parts of the frame with variable width.

- These demos enable efficient, synchronised parallel execution with ARM C user code.

- 1 motion detection video processing design.

- This demonstrates the pipelined parallel execution of HW video processing accelerators.

- HW accelerators work with fixed number of processed micro-lines (1024 micro-lines).

All demos work in parallel with single 8xSIMD EdkDSP run-time reprogrammable floating point accelerator IP developed within the ECSEL THINGS2DO project.

- The ARM Cortex A9 C programs can be compiled for in the Xilinx SDK 2015.4 environment.

- The MicroBlaze C programs can be compiled for in the Xilinx SDK 2015.4 environment.

- The PicoBlaze6 C/ASM programs for the 8xSIMD EdkDSP accelerator IP can be compiled in the embedded EdkDSP C compiler toolchain running on the TE0720-2I development module as PetaLinux 2017.1 applications.

- User can compile and optimize/customize the final system without the need to re-compile the design in Vivado 2015.4 and without the need to use the commercial SDSoC 2015.4 development system.

All demos are designed for the Trenz Electronic TE0701-06 platform with industrial grade Zynq XC7Z020-2I device on System on Module TE0720-2IF.

All demonstrated video processing algorithms have been developed, debugged and tested as SW algorithms for ARM in Xilinx SDSoC 2015.4 environment. Selected SW functions have been compiled by the Xilinx SDSoC 2015.4 system level compiler (based on the Xilinx HLS compiler) to the Vivado 2015.4 HW projects, and compiled by Vivado 2015.4 to the bitstreams for Zynq XC7Z020-2I device. The new SDSoC functions controlling the HW accelerators have been exported from the Xilinx SDSoC 2015.4 projects to the standalone Xilinx SDK 2015.4 projects as static .a libraries for the ARM Cortex A9 processor.

Package Summary

| Title | Video Processing Demonstrator with Full HD Sensor and 8xSIMD EdkDSP Accelerator IP Core |

| Download | t20i2tm4_V54_IMPORT.zip things2do_t20i2tm4_2015_4_te0701.pdf |

| License | things2do_t20i2tm4_2015_4_te0701.pdf for licensing conditions. |

| Package content | ZIP archive with precompiled Vivado 2015.4 projects demonstrating video processing demonstrator with full HD sensor and 8xSIMD EdkDSP accelerator IP core. |

| Size | ZIP file: 82760221 Bytes PDF file: 4558699 Bytes |

| Required tools & platform |

Xilinx SDK 2015.4 |

| Installation notes | See things2do_t20i2tm4_2015_4_te0701.pdf |

Result Category

| Project number | Year | RIV category | Comment |

| 7H14007 | 2018 | Gfunk | Functional sample (demo) |