# Video Processing Demonstrator with Full HD Sensor and 8xSIMD EdkDSP Accelerator IP Core

## Trenz Electronic TE0720-2IF Module, TE0701 Carrier

Jiří Kadlec, Zdeněk Pohl, Lukáš Kohout <u>kadlec@utia.cas.cz</u>, <u>xpohl@utia.cas.cz</u>, <u>kohoutl@utia.cas.cz</u> phone: +420 2 6605 2216 UTIA AV CR, v.v.i.

Revision history:

| Rev. | Date       | Author      | Description                                       |

|------|------------|-------------|---------------------------------------------------|

| 1    | 08.03.2017 | Jiří Kadlec | Evaluation package for Xilinx SDK 2015.4          |

| 2    | 30.01.2018 | Jiří Kadlec | Updated for use of the embedded EdkDSP C compiler |

|      |            |             |                                                   |

Acknowledgements:

This work has been partially supported by ENIAC JU project THINGS2DO No. 621221 and by related MEYS (CZ NFA) project 7H14007.

# **Table of Contents**

| Video Processing Demonstrator with Full HD Sensor and 8xSIMD EdkDSP Accelerator IP Core Trenz E<br>Module, TE0701 Carrier     |                   |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1. Evaluation Designs                                                                                                         | 5                 |

| 1.1 Objectives                                                                                                                |                   |

| Main objectives of this application note:                                                                                     |                   |

| Common setup for demos:                                                                                                       |                   |

| 1.2 Full HD Toshiba platform with EdkDSP Accelerator<br>Details of the video processing video chain:                          |                   |

| 1.3 Introduction to the demos                                                                                                 |                   |

| Edge detection                                                                                                                |                   |

| Motion detection<br>Frames per Second (FPS) Measurements                                                                      |                   |

| 1.4 Project sh01: EdkDSP accelerator with edge detection in single HLS accelerator                                            |                   |

| 1.5 Project sh02: EdkDSP accelerator with edge detection in two HLS accelerators                                              |                   |

| -<br>1.6 Project sh03: EdkDSP accelerator with edge detection in three HW accelerators                                        |                   |

| 1.7 Project md01: EdkDSP accelerator with motion detection in HLS accelerators                                                |                   |

| 2. Installation of the Evaluation Package                                                                                     | 15                |

| 2.1 Import of SW projects in Xilinx SDK 2015.4                                                                                |                   |

| 2.2 HW setup                                                                                                                  |                   |

| 2.3 Test demos                                                                                                                |                   |

| 2.4 Synchronisation of user C code with the video processing HW accelerators                                                  |                   |

| User defined synchronisation with parallel HW data paths (SW barrier)<br>Internal synchronisation with parallel HW data paths |                   |

| 2.5 EdkDSP C compiler API                                                                                                     |                   |

| EdkDSP C compiler                                                                                                             |                   |

| 2.6 Debug of the EdkDSP accelerator IP firmware with the In-circuit Logic Analyser                                            |                   |

| 2.7 Use of In-circuit Logic Analyser (ILA)                                                                                    |                   |

| 2.7 Ose of In-circuit Logic Analyser (ILA)                                                                                    |                   |

| 3. Conclusions                                                                                                                | 48                |

| 4. References                                                                                                                 | 49                |

| 5. Free Evaluation Version of the Package                                                                                     | 50                |

| 6. Vivado Projects with the Evaluation Version of the (8xSIMD) EdkDSP IP for the Eniac THINGS2DO P                            | roject Partners52 |

| 7. Vivado Projects with the Release Version of the 8xSIMD EdkDSP IP with no HW Limit on Number o                              | •                 |

| Disclaimer                                                                                                                    |                   |

|                                                                                                                               | _                 |

http://zs.utia.cas.cz

2/57

# Table of Figures

| Figure 1: Full HD Toshiba evaluation platform with video processing in HW and EdkDSP accelerator. | 6    |

|---------------------------------------------------------------------------------------------------|------|

| Figure 2: Project sh01 - Edge detection with single HW accelerator and EdkDSP accelerator         |      |

| Figure 3: Project sh01 - Energy per frame reduction and used HW resources.                        |      |

| Figure 4: Project sh02 - Edge detection with two HW accelerators and 1x 8xSIMD EdkDSP IP          |      |

| Figure 5: Project sh02 - Energy per frame reduction and used HW resources.                        | . 10 |

| Figure 6: Project sh03 - Edge detection with three HW accelerators and 1x 8xSIMD EdkDSP IP        | . 11 |

| Figure 7: Project sh03 - Energy per frame reduction and used HW resources.                        | . 11 |

| Figure 8: Project md01 - Motion detection with single HW accelerator and 1x 8xSIMD EdkDSP IP      | . 12 |

| Figure 9: Project md01 - Energy per frame reduction and HW resources.                             | . 12 |

| Figure 10: Project sh01 - Edge detection in 1x HW accelerator. 1x 8xSIMD EdkDSP IP                | . 13 |

| Figure 11: Project sh02 - Edge detection in 2x HW accelerators. 1x 8xSIMD EdkDSP IP               | . 13 |

| Figure 12: Project sh03 - Edge detection in 3x HW accelerator. 1x 8xSIMD EdkDSP IP                |      |

| Figure 13: Project md01 - Motion detection in 8 chained HW accelerators. 1x 8xSIMD EdkDSP IP      |      |

| Figure 14: Select the SDK Workspace                                                               | . 15 |

| Figure 15: Import Existing Projects into Workspace.                                               | . 16 |

| Figure 16: Select "Copy projects into workspace" and finish the import of all projects            | . 17 |

| Figure 17: All projects are compiled in debug mode                                                |      |

| Figure 18: USB for ARM terminal and JTAG. RS232C Pmod for MicroBlaze                              | . 20 |

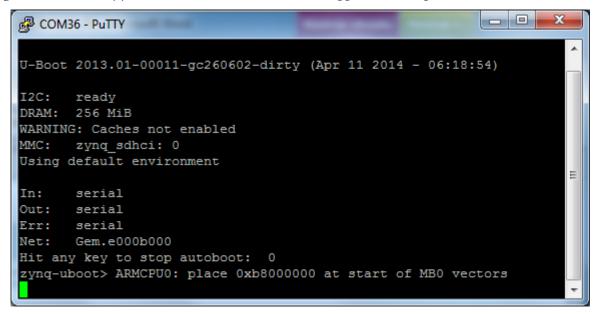

| Figure 19: Serial console. Reset board and stop autoboot by any key                               |      |

| Figure 20: Download bitstream to the PL part of Zynq.                                             |      |

| Figure 21: Select demo application for debug.                                                     | . 22 |

| Figure 22: Demo app is booted to ARM and the debugger is waiting on the first executable line     | . 23 |

| Figure 23: ARM is waiting on HW Mutex for the MicroBlaze start.                                   | . 23 |

| Figure 24: Select the MicroBlaze application (with the EdkDSP accelerator code) for debug         |      |

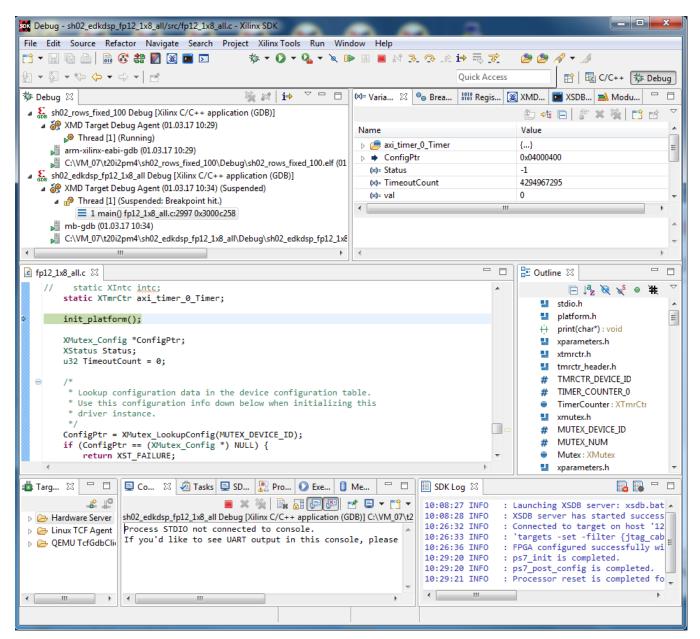

| Figure 25: MicroBlaze application is loaded and debugger stops on the first instruction.          | . 25 |

| Figure 26: ARM is running in debug mode. It indicates the number of frames per second             | . 26 |

| Figure 27: MicroBlaze is running in debug mode. It indicates MFLOPs                               | . 27 |

| Figure 28: MicroBlaze is running in release mode. It indicates MFLOPs                             | . 28 |

| Figure 29: Accelerated edge detection Full HD Toshiba sensor and Zynq with EdkDSP IP              | . 29 |

| Figure 30: Edge detection (sh02 - Sobel filters, 2 variable HW data paths) output on HDMI monitor | . 29 |

| Figure 31: ARM C function with an user defined synchronization of 2 HW accelerators               | . 30 |

| Figure 32: ARM C function with internal synchronization of a pipeline of 8 HW accelerators        | . 31 |

| Figure 33: EdkDSP C/ASM compilation of firmware on the SD card.                                   |      |

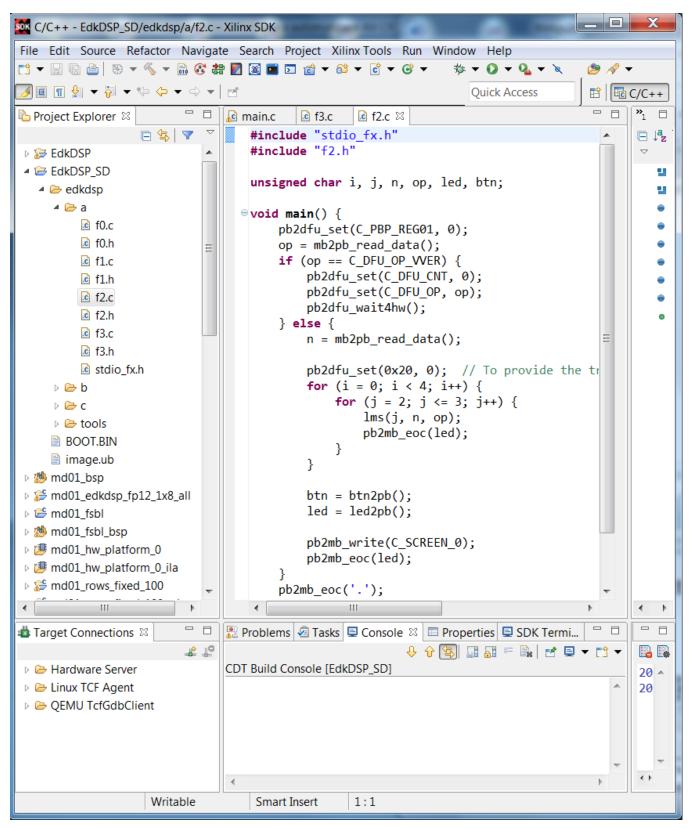

| Figure 34: C listing of the LMS filter firmware for the EdkDSP IP.                                | . 36 |

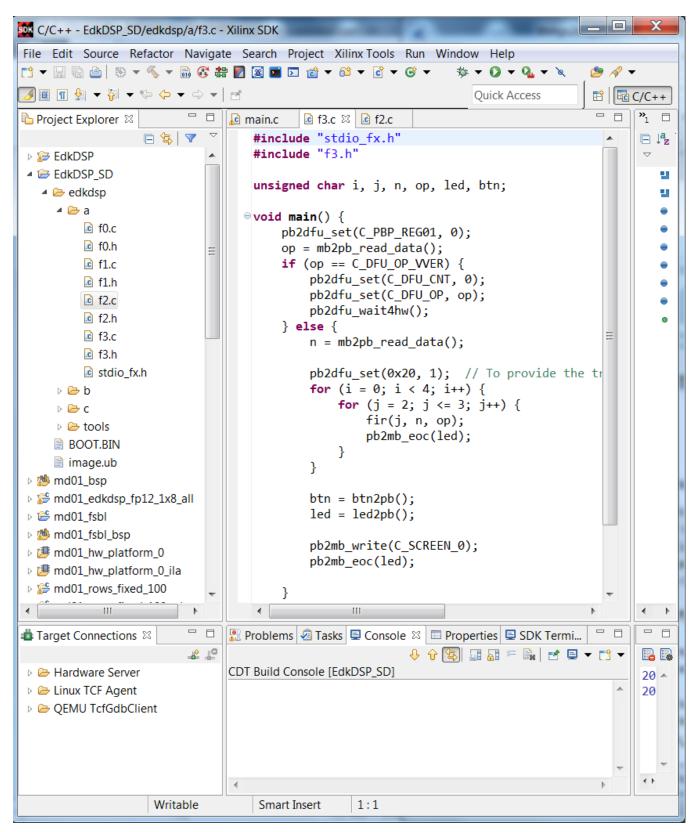

| Figure 35: C listing of the FIR filter firmware for the EdkDSP IP                                 |      |

| Figure 36: Change the default hw_platform_0 to the hw_platform_0_ila                              | . 38 |

| Figure 37: Debug ports of the (8xSIMD) EdkDSP floating point accelerator IP core.                 |      |

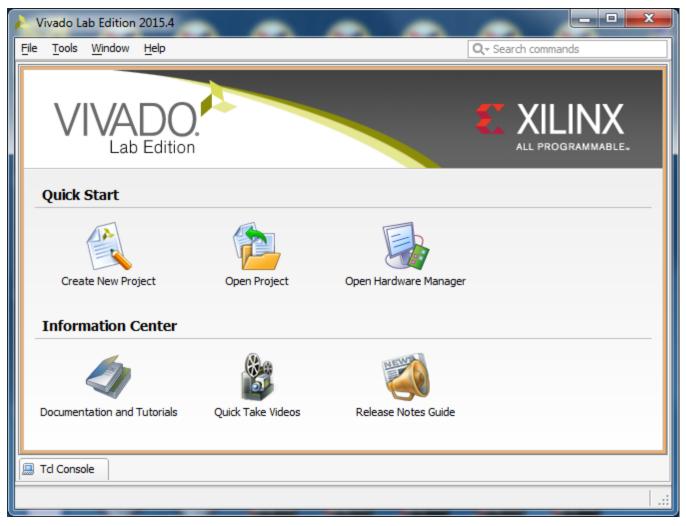

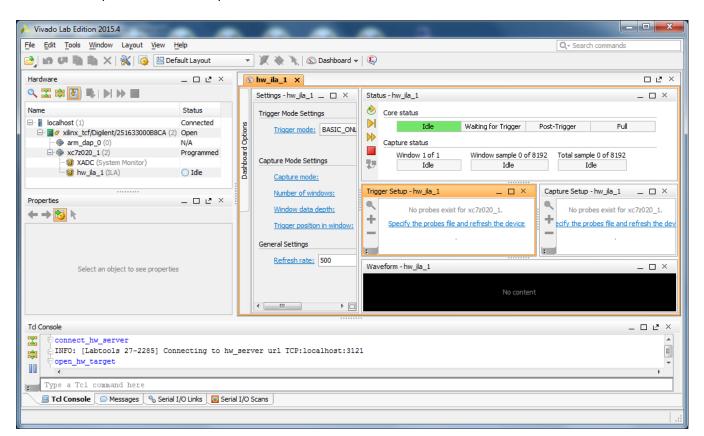

| Figure 38: Vivado Lab Edition 2015.4.                                                             | . 41 |

| Figure 39: Select Open Target                                                                     | . 42 |

| Figure 40: Select file with definition of probes present in HW                                    | . 42 |

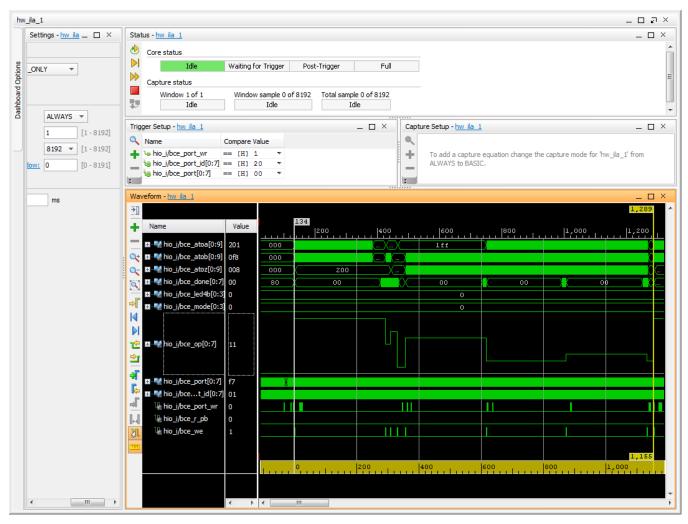

| Figure 41: FIR filter waveforms after the trigger in Vivado Lab Edition 2015.4.                   |      |

| Figure 42: LMS filter waveforms after the trigger in Vivado Lab Edition 2015.4                    |      |

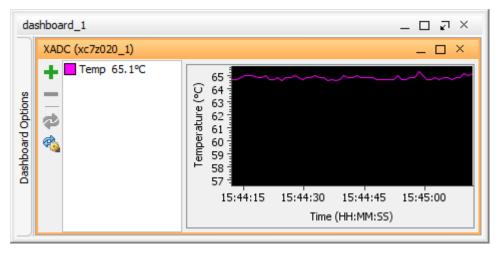

| Figure 43: Separate dashboard with display of temperature in Vivado Lab Edition 2015.4.           |      |

| Figure 44: HW accelerated motion detection algorithm - moving edges marked by red                 | . 47 |

|                                                                                                   |      |

3/57

# **Table of Tables**

| Table 1: API for MicroBlaze C code                                                       | 31 |

|------------------------------------------------------------------------------------------|----|

| Table 2: EdkDSP accelerator I/O API functions used by the PicoBlaze6 controller firmware |    |

| Table 3: (8xSIMD) EdkDSP bce_fp12_1x8_40 accelerator vector operations                   | 40 |

4/57

http://zs.utia.cas.cz

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

## 1. Evaluation Designs

### 1.1 Objectives

This application describes use of an evaluation package for the Xilinx SDK 2015.4 SW environment with these standalone, HW accelerated video processing demos designed in the Xilinx SDSoC 2015.4 environment [9]:

- 3 edge detection video processing designs (sh01, sh02, sh03) with separate HW accelerated data paths.

- These demos present the possibility to define different HW paths by different source C/C++ functions. This is important for covering of the borders lines of the parallel processed parts of the frame.

- $\circ$   $\;$  HW accelerators can process parts of the frame with variable width.

- These demos enable efficient, synchronised parallel execution with ARM C user code.

- 1 motion detection video processing design (md01).

- This demonstrates the pipelined parallel execution of HW video processing accelerators.

- HW accelerators work with fixed number of processed micro-lines (1080 micro-lines).

All demos work in parallel with single 8xSIMD EdkDSP run-time reprogrammable floating point accelerator IP developed within the ECSEL THINGS2DO project.

- The ARM Cortex A9 C programs can be compiled for in the Xilinx SDK 2015.4 environment.

- The MicroBlaze C programs can be compiled for in the Xilinx SDK 2015.4 environment.

- The PicoBlaze6 C/ASM programs for the 8xSIMD EdkDSP accelerator IP can be compiled in the embedded EdkDSP C compiler toolchain running on the TE0720-2I development module as PetaLinux 2017.1 applications.

- User can compile and optimize/customize the final system without the need to re-compile the design in Vivado 2015.4 and without the need to use the commercial SDSoC 2015.4 development system.

All demos are designed for the Trenz Electronic TE0701-06 platform [3] with industrial grade Zynq XC7Z020-2I device on System on Module TE0720-2IF [1].

All demonstrated video processing algorithms have been developed, debugged and tested as SW algorithms for ARM in Xilinx SDSoC 2015.4 environment [9]. Selected SW functions have been compiled by the Xilinx SDSoC 2015.4 system level compiler (based on the Xilinx HLS compiler) to the Vivado 2015.4 HW projects, and compiled by Vivado 2015.4 [8] to the bitstreams for Zynq XC7Z020-2I device. The new SDSoC functions controlling the HW accelerators have been exported from the Xilinx SDSoC 2015.4 projects to the standalone Xilinx SDK 2015.4 [8] projects as static .a libraries for the ARM Cortex A9 processor.

#### Main objectives of this application note:

- To demonstrate how to install, compile, modify and use the enclosed SW projects in the SDK 2015.4 [8].

- To demonstrate the HW accelerated video processing algorithms and the energy per pixel reduction in comparison to the original SW versions.

- To demonstrate parallel execution of predefined video processing HW paths with C user code on ARM.

- To demonstrate HW accelerated video processing working in parallel with the 8xSIMD EdkDSP run-time reprogrammable floating point accelerator IP core.

5/57

http://zs.utia.cas.cz

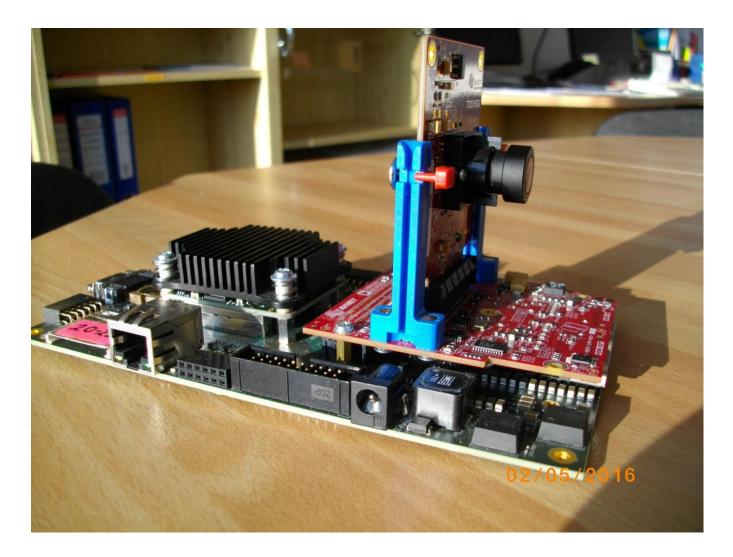

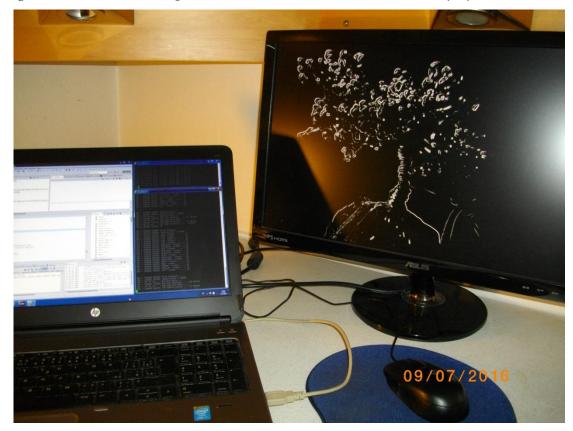

*Figure 1:* Full HD Toshiba evaluation platform with video processing in HW and EdkDSP accelerator.

#### Common setup for demos:

- The ARM Cortex A9 processor of Xilinx Zynq device XC7Z020-2I executes standalone C application programs performing initialisation and synchronisation of the HW accelerated video processing chains.

- Enclosed C programs can be modified by the user and recompiled in Xilinx SDK 2015.4.

- Full HD Toshiba sensor with Full HD resolution 1920x1080p60 provides raw colour video data.

- Data are processed in HW into the YCrCb 4:2:2 (16 bit per pixel) format and stored by video DMA (VDMA) controller to input video frame buffers (VFBs) reserved in the DDR3.

- HW DMA controller(s) send data from the input VFBs to the processing HW accelerators in the programmable logic (PL) part of Zynq.

- Another HW DMA controller(s) send processed data from HW to output VFBs in DDR3.

- Second part of the HW VDMA writes processed data to the Full HD HDMI display with Full HD resolution 1920x1080p60.

## 1.2 Full HD Toshiba platform with EdkDSP Accelerator

This application note describes HW platform performing integration of the runtime reprogrammable 8xSIMD EdkDSP floating point accelerator with edge detection and motion detection video processing of raw data from the Full HD Toshiba colour video sensor with fixed Full HD resolution 1920x1080p60.

6/57

- The Xilinx Zynq device xc7z020-2I has two ARM Cortex A9 processors (operating at 766.7 MHz). Memory controller provides interface to DDR3 memory access ports. The Zynq device provides also the programmable logic area used for:

- UTIA EdkDSP (8xSIMD) floating point accelerator (operating at 120 MHz) connected to Xilinx MicroBlaze 32 bit processor. The MicroBlaze works with 100 MHz clock.

- Input chain of video processing IPs connects Full HD Toshiba video sensor with Full HD resolution 1920x1080p60 to the input video frame buffers. The sensor pixel clock is set to 148.5 MHz.

- The input video DMA (VDMA) controller operates at 150 MHz.

- Part of PL is reserved for the HLS HW accelerators and data movers defined in Xilinx SDSoC 2015.4 environment. These accelerators are controlled from ARM Cortex A9 C programs in SDK 2015.4 C projects. These HLS accelerators are work with 150 MHz clock.

- The output VDMA controller operates also with the 150 MHz clock.

- Finally, chain of output video processing IPs connects the output frame buffer with pixel clock 148.5 MHz to the HDMI display with the Full HD resolution 1920x1080p60.

- UTIA EdkDSP is 8xSIMD floating point accelerator IP. It is reprogrammable in runtime by change of firmware of build in PicoBlaze6 8bit controller. It takes the role of an scheduler of vector operations performed in the EdkDSP is 8xSIMD floating point processor data paths. This scheduler is programmed by simple C programs compiled by simple C compiler and assembler, respecting the minimal resources of the PicoBlaze6 controller.

- UTIA EdkDSP is 8xSIMD floating point accelerator IP is controlled by the 32bit MicroBlaze processor. The MicroBlaze processor executes C programs from the DDR3 memory. Complex C algorithms can benefit from execution of selected operations efficiently on the EdkDSP coprocessor connected to the MicroBlaze via local dual ported memories. MicroBlaze C programs can take benefit of overlap of its data communication from DDR3 to the EdkDSP dual-ported memories with parallel computations in the EdkDSP accelerator.

- Platform also includes the video processing chain consisting of IPs controlled by ARM Cortex A9 processor.

- ARM Cortex A9 processor of Xilinx Zynq performs initialisation and synchronisation of the video processing chain. Program and the FPGA bitstream file is downloaded to the board from the Xilinx SDK 2015.4 via USB JTAG. The program is located in the 1GB DDR3 memory on the Zynq SoM. System can be also started directly from the SD card. ARM processor initiates the IP cores in the programmable logic (PL) part of the Zynq. It also initiates the Full HD Toshiba video sensor and the video output to a monitor with Full HD 1920x1080p60 resolution.

#### Details of the video processing video chain:

- Data are provided by the Full HD Toshiba video sensor with the Full HD 1920x1080p60 resolution. The raw video data received from video sensor are coded in Bayer format.

- Data are processed into the YCrCb 4:2:2 format (this is 16 bit per pixel) and stored by Video DMA (VDMA) to the input video frame buffers (VFBs) defined in the DDR3.

- HW DMA controller(s) send data from/to the VFBs to the processing accelerators. Clock is 150 MHz.

The evaluation designs with HW accelerators have been created from C/C++ functions tested in the Xilinx SDSoC 2015.4 system level compiler.

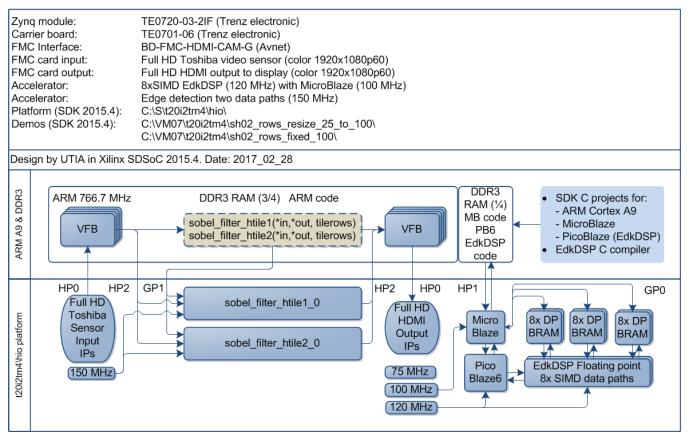

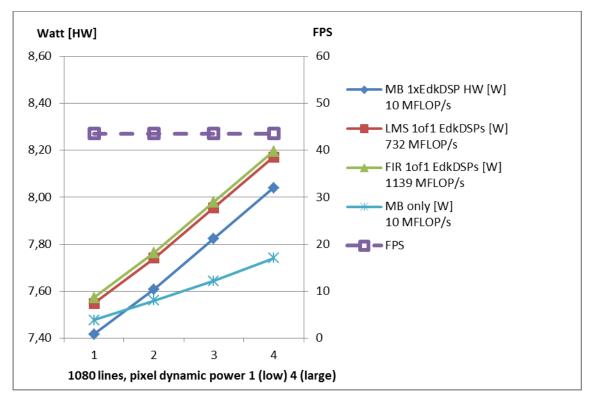

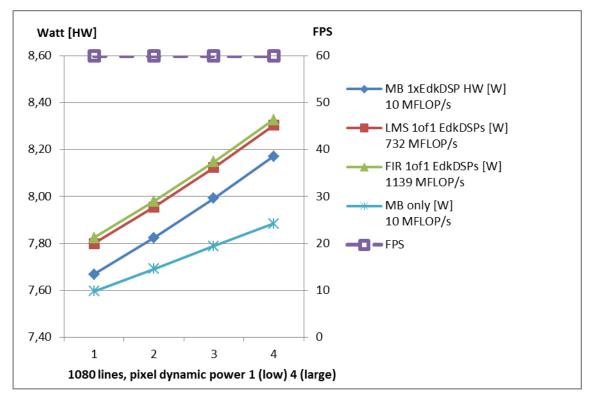

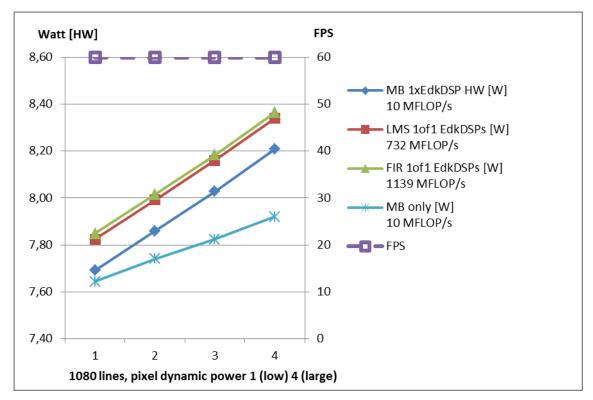

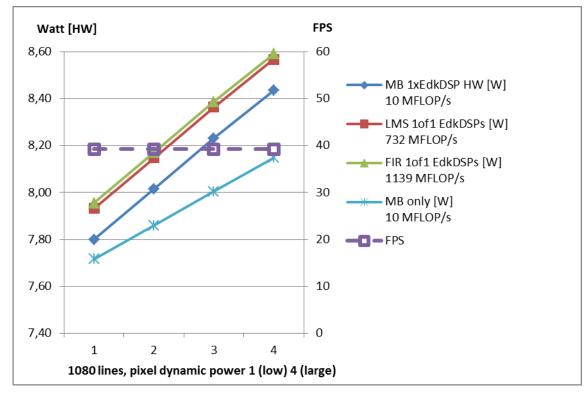

Projects described in the next section summarise the energy per frame measured on the platform for different HW accelerated image processing algorithms as defined by the individual C projects in these four main configurations:

7/57

signal processing

- 2. The MicroBlaze with EdkDSP coprocessor computes LMS adaptive filter in floating point (in parallel to the dedicated video processing accelerator chain).

- 3. The MicroBlaze computes in SW (only with its floating point unit) the FIR or LMS filter (in parallel to the dedicated video processing accelerator chain) but EdkDSP accelerator is not used.

- 4. The MicroBlaze is present and computes in SW (only with its floating point unit) the FIR or LMS filter. The EdkDSP is not present in the PL at all. The dedicated video processing accelerator chain processes the video from the Full HD Toshiba video sensor.

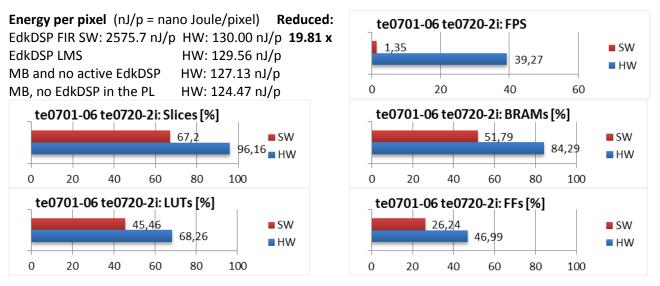

The figures provide comparison of the energy/pixel consumed by the complete system in case of computation in ARM. C/C++ code was compiled with -O3 optimisation (but without NEON) in the SDSoC 2015.4 environment [9] with no video processing HW accelerators present and the EdkDSP computing FIR filter. It is labled as "SW".

This "SW" energy/pixel result is compared with the energy/pixel consumed by s complete system in case of HW accelerated video processing and different modes of the EdkDSP accelerator: (1) FIR or (2) LMS on EdkDSP or (3) on MicroBlaze with EdkDSP present but not used of, finally, (4) with computation of FIR or LMS on MicroBlaze with no EdkDSP accelerator HW logic present in the PL part of the Zynq device.

### **1.3 Introduction to the demos**

#### **Edge detection**

The edge detection algorithm produces B/W video stream. Edges in each frame are marked as white and remaining part of the figure is set as black. The edges are detected by a Sobel filter. Each pixel is filtered by a 3x3 2D FIR filter. A nonlinear decision on the output of the filter provides decision if the pixel is part of an edge or not. All computations are performed in fixed point. Input to the Sobel filter is the video signal with each pixel converted to the monochrome 8bit format.

Demos **sh01**, **sh02** and **sh03** provide HW accelerated computation of edge detection with 1, 2 or 3 parallel HW data paths. Computation of horizontal border line is resolved in case of sh02 and sh03. All these demos support synchronised parallel execution of user defined C code on ARM while the HW data paths perform accelerated video processing. HW demos use 1, 2 or 3 DMA HW channels as input from DDR3 to 1, 2 or 3 Sobel filters. Another 1, 2 or 3 DMA HW channels support output from Sobel filters to the DDR3. Demos are linked with static libraries libsh01.a, libsh02.a or libsh03.a. Zynq PL resources and the accelerations reached for these HW designs are summarised in sections 1.4, 1.5 and 1.6.

#### **Motion detection**

The motion detection algorithm detects and performs visualisation of moving edges. The moving edges are identified by two Sobel filters performing FIR filtering (similar to the above described edge detection) on pixels with identical coordinates but from two subsequent video frames. A difference of these filtered results is computed a noise in that signal is filtered by a Median filter. Resulting signal is used for the nonlinear binary decision if the analysed pixel is part of a moving edge or not. If the pixel is part of a moving edge, it is assigned red colour and merged with the original colour video signal. Resulting output video signal is unchanged, with the exception of red colour marked moving edges.

Demo **md01** provides accelerated HW computation with one parallel HW data path. HW demo uses 2 DMA HW channels for reading from two sub sequent video frame buffers; both located both in the DDR3, to pass the data to the video processing chain of accelerators performing the motion detection. Another DMA HW channel performs parallel write of results to the DDR3. Demo is linked with static library libmd01.a. Zynq PL resources and accelerations reached for these HW designs are summarised in section 1.7.

8/57

#### Frames per Second (FPS) Measurements

We report the measured frames per second (FPS) reached by the accelerator and the FPS reached by the initial SW implementation on ARM in the SDSoC 2015.4. In case of SW implementation –O3 optimisation was used. The Full HD Toshiba input and the HDMI output data movements are supported by the dedicated VDMA HW channels in all cases.

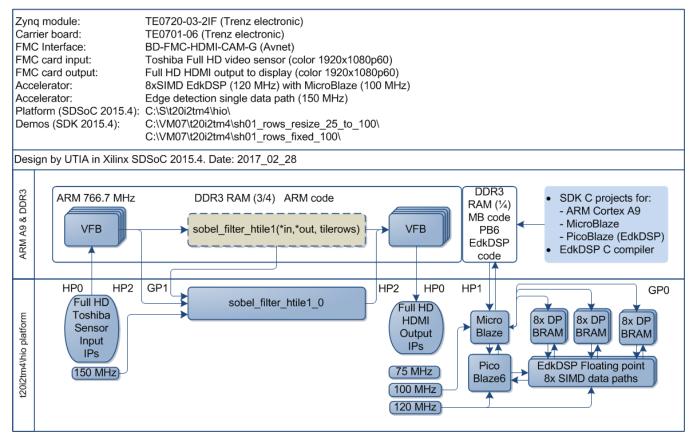

#### 1.4 Project sh01: EdkDSP accelerator with edge detection in single HLS accelerator

*Figure 2:* Project sh01 - Edge detection with single HW accelerator and EdkDSP accelerator.

Figure 3: Project sh01 - Energy per frame reduction and used HW resources.

| signal processing |      | http://zs.utia.cas.cz |

|-------------------|------|-----------------------|

|                   | 9/57 |                       |

ŪΠA

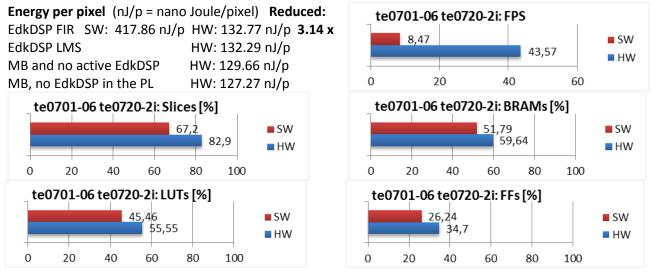

## 1.5 Project sh02: EdkDSP accelerator with edge detection in two HLS accelerators

Figure 4: Project sh02 - Edge detection with two HW accelerators and 1x 8xSIMD EdkDSP IP.

Figure 5: Project sh02 - Energy per frame reduction and used HW resources.

## 1.6 Project sh03: EdkDSP accelerator with edge detection in three HW accelerators

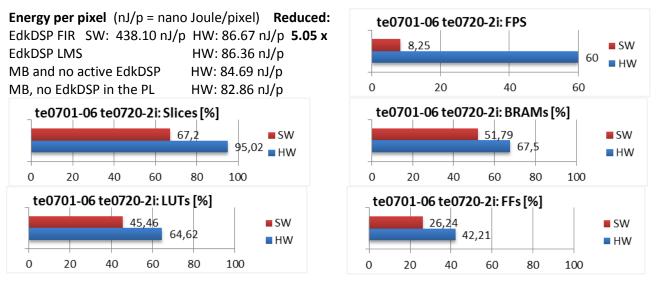

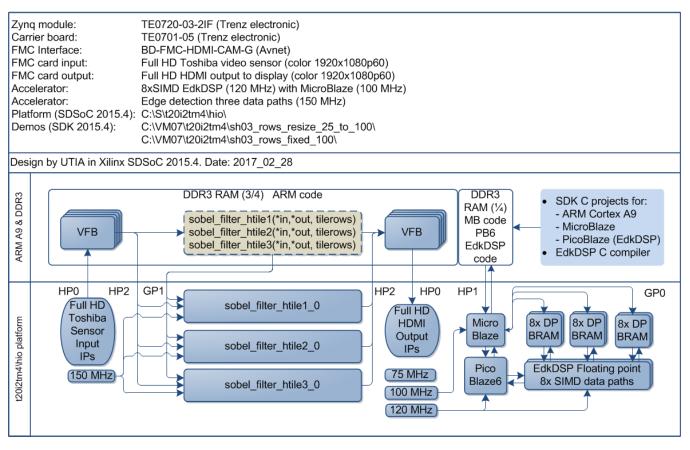

Figure 6: Project sh03 - Edge detection with three HW accelerators and 1x 8xSIMD EdkDSP IP.

*Figure 7:* Project sh03 - Energy per frame reduction and used HW resources.

© 2018 ÚTIA AV ČR, v.v.i. All disclosure and/or reproduction rights reserved

## 1.7 Project md01: EdkDSP accelerator with motion detection in HLS accelerators

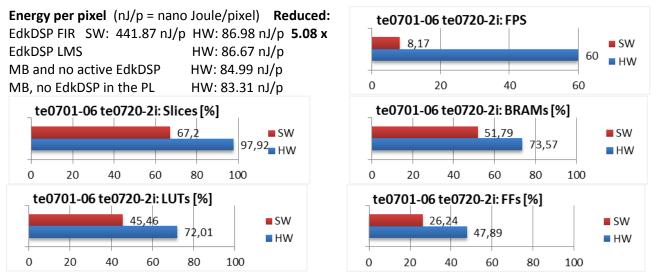

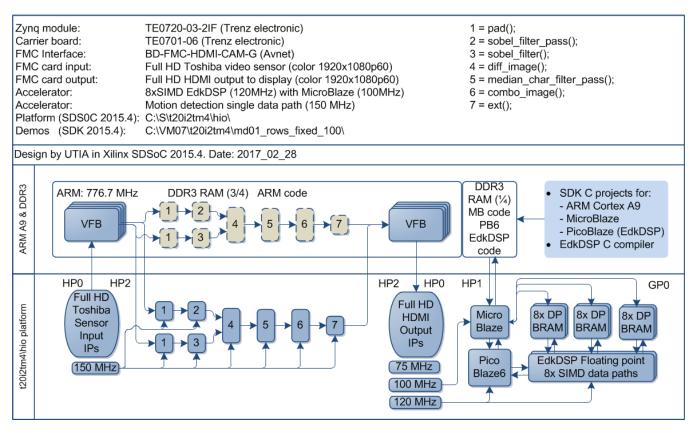

Figure 8: Project md01 - Motion detection with single HW accelerator and 1x 8xSIMD EdkDSP IP.

*Figure 9:* Project md01 - Energy per frame reduction and HW resources.

Figure 10: Project sh01 - Edge detection in 1x HW accelerator. 1x 8xSIMD EdkDSP IP.

Figure 11: Project sh02 - Edge detection in 2x HW accelerators. 1x 8xSIMD EdkDSP IP.

Figure 12: Project sh03 - Edge detection in 3x HW accelerator. 1x 8xSIMD EdkDSP IP.

Figure 13: Project md01 - Motion detection in 8 chained HW accelerators. 1x 8xSIMD EdkDSP IP

http://zs.utia.cas.cz

14/57

## 2. Installation of the Evaluation Package

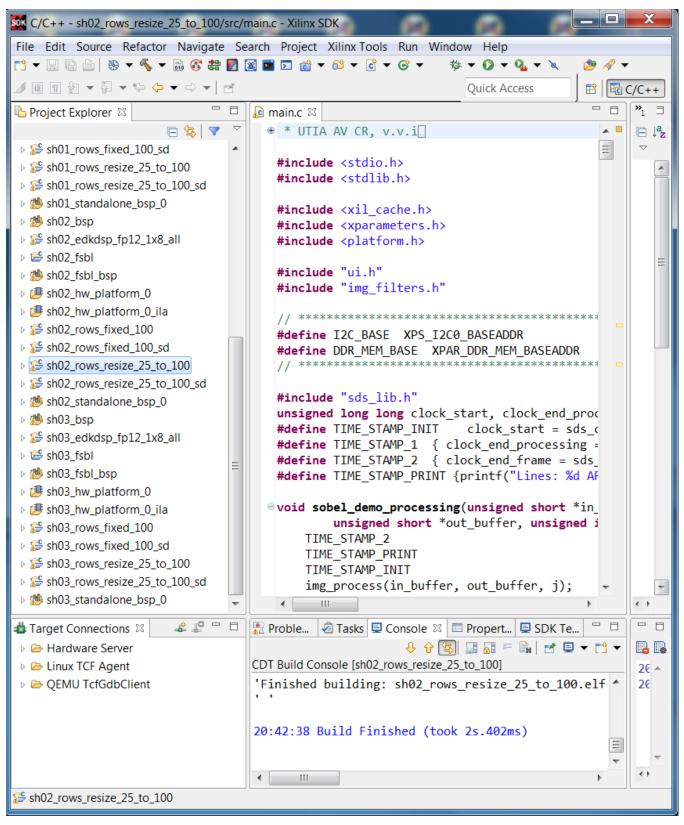

## 2.1 Import of SW projects in Xilinx SDK 2015.4

Unzip the evaluation package to the directory C:\VM\_07\t20i2tm4\_V54\_IMPORT

Create empty directory for Xilinx SDK workspace. C:\VM\_07\t20i2tm4

Start Xilinx SDK 2015.4 and select the directory for the SDK 2015.4 workspace. See Figure 14 Select C:\VM\_07\t20i2tm4

| Sox Workspace Launcher                                                                                                | ×   |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Select a workspace                                                                                                    |     |

| Xilinx SDK stores your projects in a folder called a workspace.<br>Choose a workspace folder to use for this session. |     |

| Workspace: C:\VM_07\t20i2pm4    Brows                                                                                 | ie  |

| Use this as the default and do not ask again OK Canc                                                                  | :el |

Figure 14: Select the SDK Workspace.

15/57

HW and SW projects can be imported into SDK now. Select:

#### File -> Import -> General -> Existing Projects into Workspace

Click on Next button. See Figure 15.

http://zs.utia.cas.cz

| sok Import                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Select<br>Choose import source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2      |

| Select an import source:<br>type filter text<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>General<br>Gene |        |

| ▷ ➢ Run/Debug ▷ ➢ Team ▷ ➢ Tracing ○ < Back Next > Finish                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Cancel |

*Figure 15:* Import Existing Projects into Workspace.

Type the directory with projects to be imported. See Figure 16.

#### C:\VM\_07\t20i2tm4\_V54\_IMPORT

Set the "Copy projects into workspace" check box.

Click on Finish button. See Figure 16.

Process of compilation will start automatically. This first compilation of all SDK SW projects can take several minutes to finish. It should finish without errors.

16/57

http://zs.utia.cas.cz

| Sok Import                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                          | •                                                                                                                        | -    |                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------|

| Import Projects<br>Select a directory to sear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rch for existing Eclipse p | projects.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                            |                                                                                                                          |      |                                                           |

| <ul> <li>Select root directory:</li> <li>Select archive file:</li> <li>Projects:</li> <li>EdkDSP (C:\VM_07</li> <li>EdkDSP_SD (C:\VM_07</li> <li>EdkDSP_SD (C:\VM_07</li> <li>md01_bsp (C:\VM_07</li> <li>md01_edkdsp_fp1</li> <li>md01_fsbl (C:\VM_07</li> <li>md01_fsbl_bsp (C:\VM_07</li> <li>md01_hw_platform</li> <li>md01_hw_platform</li> <li>md01_rows_fixed_</li> <li>md01_rows_fixed_</li> <li>sh01_bsp (C:\VM_07</li> <li>sh01_edkdsp_fp12</li> <li>sh01_fsbl_bsp (C:\VM_07</li> <li>sh01_fsbl_bsp (C:\VM_07</li> <li>sh01_fsbl_bsp (C:\VM_07</li> <li>sh01_fsbl_bsp (C:\VM_07</li> <li>sh01_fsbl_bsp (C:\VM_07</li> <li>sh01_hw_platform</li> <li>sh01_hw_platform</li> <li>sh01_hw_platform</li> <li>sh01_hw_platform</li> </ul> |                            | 54_IMPORT<br>54_IMPORT<br>CORT\EdkDSP)<br>PORT\EdkDSP_SD<br>DI2tm4_V54_IMPO<br>DI2tm4_V54_IMPORT<br>MPORT\md01_fsb<br>IMPORT\md01_fsb<br>IMPORT\md01_fsb<br>IMPORT\md01_fsb<br>IMPORT\md01_fsb<br>IMPORT\md01_fsb<br>IMPORT\sh01_fsb<br>IMPORT\sh01_fsb<br>MPORT\sh01_fsb<br>V54_IMPORT\sh0<br>m4_V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54_IMPORT\sh0<br>-V54 | DRT\md01_edkd<br>sbl_bsp)<br>nd01_hw_platfor<br>T\md01_hw_plat<br>nd01_rows_fixed<br>T\md01_rows_fi<br>T\md01_standalo<br>RT\sh01_edkdsp<br>_bsp)<br>D1_hw_platform_<br>\sh01_hw_platfo<br>01_rows_fixed_1 | rm_0)<br>tform_0_ila)<br>d_100)<br>ixed_100_sd)<br>one_bsp_0)<br>o_fp12_1x8_all)<br>o_fp12_1x8_all)<br>_0)<br>orm_0_ila) |      | Browse<br>Browse<br>Select All<br>Deselect All<br>Refresh |

| Options          Search for nested projects         Copy projects into workspace         Working sets         Add project to working sets         Working sets:         Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            |                                                                                                                          |      |                                                           |

| ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | < Back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Next >                                                                                                                                                                                                     | Fi                                                                                                                       | nish | Cancel                                                    |

Figure 16: Select "Copy projects into workspace" and finish the import of all projects.

Figure 17: All projects are compiled in debug mode.

The SDK 2015.4 tool compiles SW of all imported demos for the default debug mode. This will take several minutes.

## 2.2 HW setup

HW setup is based on commercially accessible components [1], [2], [3], [4], [5], [6]:

TE0720-2IF; Part: XC7Z020-2CLG484I; 1 GByte DDR; Industrial Grade (-40°C to +85°C) [1].

Heatsink for TE0720, spring-loaded embedded [2].

TE0701 Carrier Board for Trenz Electronic 7 Series [3].

AES-FMC-HDMI-CAM-G FMC card with HDMI I/O and CAM interface [4].

FULL HD TOSHIBA Color Image Sensor Camera Module [5].

PmodRS232: Serial converter & interface [6].

See the technical reference manuals (TRM) for the description of the TE0720-02-2IF or TE0720-03-2IF module revision [1] and TE0701-04, TE0701-05 or TE0701-06 revision of carrier boards [3].

#### Set the TE0701 carrier board switches and jumpers for the TE0720-03-2IF module as follows:

- Set switch S3 TE701-04 switch S3: 1=ON 2=OFF 3=ON 4=OFF TE701-05 switch S3: 1=ON 2=OFF 3=ON 4=OFF TE701-06 switch S3: 1=ON 2=OFF 3=ON 4=OFF

- Set jumpers to generate FMC\_VADJ=2.5V TE701-04: (VIOTA=2.5V VIOTB=FMC\_VADJ=VADJ=2.5V) J17: connect 2-3; J21: connect 2-3 TE701-05: (VIOTA=2.5V VIOTB=FMC\_VADJ=VADJ=2.5V) J17: connect 2-3; J21: connect 2-3 TE701-06: (VIOTA=VIOTB=FMC\_VADJ=VADJ=2.5V) J16: closed; J17: open; J21: connect 2-3

- Set switch S4 (only in case of TE701-06) TE701-06 switch S4: (set FMC\_VADJ=2.5V as power source): 1=OFF 2=ON 3=ON 4=OFF

The TE0720-2IF Zynq device works with all IO-bank supply-voltages 2.5V. It is highly recommended to set switches of the TE0701 carrier board and measure the PL IO-bank supply-voltage before mounting of the module on TE0701. See locations and switch positions in the TE0701 TRMs [3].

#### Note:

In case of TE0701-04 or TE0701-05, the PmodRS232 serial converter & interface [6] is powered by 3.3V.

In case of the TE0701-06 [3], the PmodRS232 serial converter & interface [6] will be powered by VIOTA=2.5V of the PMOD header J5. This voltage is below the power supply specification (3V ... 5V) of the PmodRS232 serial converter. Based on our experiments the PmodRS232 serial converter works OK with the power supply 2.5V.

#### 2.3 Test demos

To test demos follow these steps:

- Insert the Full HD Toshiba video sensor to the connector on the AES-FMC-HDMI-CAM-G board.

- Connect HDMI (or DVI) monitor by HDMI cable to the HDMI OUT on the AES-FMC-HDMI-CAM-G card.

- Switch the monitor ON.

- Connect the carrier board by USB-to-microUSB cable to PC to support JTAG serial link and the standard serial terminal.

- Connect the PmodRS232 serial converter & interface module to the carrier board as indicated in Figure 18. Connect the RS232 cable to COM1 serial terminal of your PC. This serial line will support serial terminal for the MicroBlaze processor.

19/57

• Connect power supply (DC 12V).

signal processing

• Open and configure the standard serial terminal client (PuTTY or similar) on PC for the ARM serial terminal (USB emulated). Set up:

Speed: 115200 baud; Data bits: 8; Stop bits: 1; Parity: None; Flow control: None.

• Open and configure the standard serial terminal client (PuTTY or similar) on PC for MicroBlaze It is COM1. Set up:

Speed: 115200 baud; Data bits: 8; Stop bits: 1; Parity: None; Flow control: None.

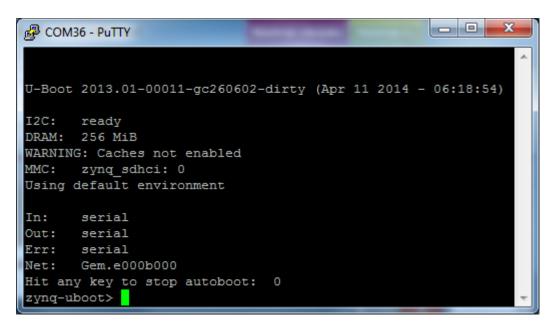

- Reset the board. Board will start first stage boot loader from internal flash as set up by Trenz Electronic. It writes messages to the serial terminal. On request, "Hit any key to stop autoboot" press any key to stop the auto-boot of Linux.

- If you need to switch-off the power, close first the serial terminal on the PC. This will help to avoid problems with lost communication.

*Figure 18:* USB for ARM terminal and JTAG. RS232C Pmod for MicroBlaze.

20/57

http://zs.utia.cas.cz

Figure 19: Serial console. Reset board and stop autoboot by any key.

Download bitstream to the board. Demo sh02\_rows\_resize\_25\_to\_100 will be used as an example. The bitstream.bit file for demo sh02 is located in the directory: C:\VM\_07\t20i2tm4\sh02\_hw\_platform\_0

Select Program to download the bitstream to the PL part of Zynq via the USB cable in JTAG mode.

| Program FPGA        |                                                                                                                                              | X                                                                  |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|

| Program FPGA        | Program FPGA                                                                                                                                 |                                                                    |  |  |  |  |

|                     | BMM/MMI file is not specified, BRAM will not be initialized. To generate it, use command     write_mem_info <filepath> in Vivado.</filepath> |                                                                    |  |  |  |  |

| - Hardware Configur | ation                                                                                                                                        |                                                                    |  |  |  |  |

| Hardware Platform   | : sh02_hw                                                                                                                                    | _platform_0                                                        |  |  |  |  |

| Connection:         | Local                                                                                                                                        | ▼ New                                                              |  |  |  |  |

| Device:             | Auto De                                                                                                                                      | tect Select                                                        |  |  |  |  |

| Bitstream:          | C:\VM_0                                                                                                                                      | C:\VM_07\t20i2tm4\sh02_hw_platform_0\hio_wrapper.bit Search Browse |  |  |  |  |

| Partial Bitstream   | ı                                                                                                                                            |                                                                    |  |  |  |  |

| BMM/MMI File:       |                                                                                                                                              | Search Browse                                                      |  |  |  |  |

| Software Configura  | ation                                                                                                                                        |                                                                    |  |  |  |  |

| Processor           |                                                                                                                                              | ELF/MEM File to Initialize in Block RAM                            |  |  |  |  |

| microblaze_0        |                                                                                                                                              | bootloop                                                           |  |  |  |  |

| ?                   |                                                                                                                                              | Program Cancel                                                     |  |  |  |  |

Figure 20: Download bitstream to the PL part of Zynq.

| sok Debug Configurations                                                                                                                                                                                                                                                                              |                                                                           |                                          | ×                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------|

| Create, manage, and run configurations                                                                                                                                                                                                                                                                |                                                                           |                                          | Ť.                                                 |

| Yerformance Analysis         Yerformance Analysis         Target Communication Framework         Xilinx C/C++ application (GDB)         Sh02_rows_fixed_100 Debug         Xilinx C/C++ application (System De         Xilinx C/C++ application (System De         Xilinx C/C++ application (System De | Debug Type: Standalone Applic<br>Connection: Local<br>Device: Auto Detect | ion ison ison ison ison ison ison ison i | Search Browse<br>Search Browse<br>ng the debugger. |

| ← Ⅲ      →     Filter matched 6 of 16 items                                                                                                                                                                                                                                                           |                                                                           | Appl                                     | y Revert                                           |

| 0                                                                                                                                                                                                                                                                                                     |                                                                           | Deb                                      | oug Close                                          |

Figure 21: Select demo application for debug.

22/57

http://zs.utia.cas.cz

Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

| Son Debug - sh02_rows_fixed_100/src/main.c - Xilinx SDK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| File Edit Source Refactor Navigate Search Project Xilinx Tools Run Wi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ndow Help                                                   |  |  |  |