Akademie věd České republiky Ústav teorie informace a automatizace AV ČR, v.v.i.

# SW Defined Floating Point 8xSIMD EdkDSP IP Serving for Adaptive Noise Cancellation

### TE0720-2IF Module and TE0701 Carrier Board

Jiří Kadlec, Zdeněk Pohl, Lukáš Kohout

<u>kadlec@utia.cas.cz</u>, <u>xpohl@utia.cas.cz</u>, <u>kohoutl@utia.cas.cz</u> phone: +420 2 6605 2216 UTIA AV CR, v.v.i.

Revision history:

| Rev. | Date       | Author      | Description            |

|------|------------|-------------|------------------------|

| 1    | 01.10.2017 | Jiří Kadlec | Initial draft.         |

| 2    | 12.01.2018 | Jiří Kadlec | Ready for the release. |

|      |            |             |                        |

|      |            |             |                        |

|      |            |             |                        |

|      |            |             |                        |

Acknowledgements:

This work has been partially supported by ENIAC JU project THINGS2DO No. 621221 and by related MEYS (CZ NFA) project 7H14007.

## **Table of Contents**

| SW Defined Floating Point 8xSIMD EdkDSP IP Serving for Adaptive Noise Cancellation<br>Carrier Board |    |

|-----------------------------------------------------------------------------------------------------|----|

| 1. EdkDSP IP Core - Introduction                                                                    | 4  |

| 2. EdkDSP IP Core – Implementation Details                                                          | 6  |

| 3. EdkDSP IP Core – PicoBlaze6 C Application Interface Functions                                    |    |

| 4. EdkDSP IP Core – MicroBlaze C Application Interface Functions                                    |    |

| 5. EdkDSP IP Core – Integration with dual core ARM A9 Linux                                         |    |

| 6. Setup of Hardware                                                                                | 19 |

| 7. Installation and Use of Base Evaluation Package                                                  | 21 |

| 8. Installation and Use of Extended Evaluation Package                                              |    |

| 9. References                                                                                       | 50 |

| 10. Base Evaluation Package                                                                         | 51 |

| 11. Extended Evaluation Package for THINGS2DO partners                                              | 52 |

| Disclaimer                                                                                          | 54 |

2/54

http://zs.utia.cas.cz

# **Table of Figures**

| Figure 1: Tester of 8xSIMD EdkDSP floating point accelerator IP core.       6         Figure 2: 8xSIMD EdkDSP floating point accelerator IP core.       8         Figure 3: Internal details of (8xSIMD) EdkDSP floating point accelerator IP core.       8         Figure 4: (8xSIMD) Edk part and DSP part of the EdkDSP floating point accelerator IP core.       10 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • •                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 4: (8xSIMD) Edk part and DSP part of the EdkDSP floating point accelerator IP core                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 5: TE701 carrier board with TE0720-2IF Zyng module                                                                                                                                                                                                                                                                                                               |

| Figure 6: MiniUSB cable and MicroUSB cable for the Pmod USBUART                                                                                                                                                                                                                                                                                                         |

| Figure 7: Release demo t01_s. ARM and 8xSIMD EdkDSP terminal output                                                                                                                                                                                                                                                                                                     |

| Figure 8: Release demo t01_s. Vivado Lab Tool is open                                                                                                                                                                                                                                                                                                                   |

| Figure 9: Release demo t01_s. Probes file is specified. Trigger conditions are set                                                                                                                                                                                                                                                                                      |

| Figure 10: Release demo t01_s. Details of the 8xSIMD EdkDSP LMS filter computation                                                                                                                                                                                                                                                                                      |

| Figure 11: Release demo t01_s. Details of the 8xSIMD EdkDSP FIR filter computation                                                                                                                                                                                                                                                                                      |

| Figure 12: Release demo t01_s. Stanalone demo supports measurements of the chip temperature 29                                                                                                                                                                                                                                                                          |

| Figure 13: Release demo t01_I. Linux start                                                                                                                                                                                                                                                                                                                              |

| Figure 14: Release demo t01_I. Login, Compilation of firmware in the EdkDSP C Compiler                                                                                                                                                                                                                                                                                  |

| Figure 15: Release demo t01_I. Program and start 8xSIMD EdkDSP demo                                                                                                                                                                                                                                                                                                     |

| Figure 16: Create new SDK 2017.1 workspace                                                                                                                                                                                                                                                                                                                              |

| Figure 17: Import the extended evaluation package projects into the SDK Workspace                                                                                                                                                                                                                                                                                       |

| Figure 18: SDK compiles MicroBlaze SW projects for the standalone debug target                                                                                                                                                                                                                                                                                          |

| Figure 19: Debug demo t01_I. Execution of the ./t01_s.elf example from the SD card                                                                                                                                                                                                                                                                                      |

| Figure 20: Debug demo t01_s. Open project edkdsp_fp12_1x8_s for debug                                                                                                                                                                                                                                                                                                   |

| Figure 21: Debug demo t01_s. Start the free-run from the debugger                                                                                                                                                                                                                                                                                                       |

| Figure 22: Debug demo t01_s. Arm started EdkDSP and runs SDSoC akcelerátor demo                                                                                                                                                                                                                                                                                         |

| Figure 23: Debug demo t01_s. MicroBlaze project output (Compiled for Debug)                                                                                                                                                                                                                                                                                             |

| Figure 24: Compiled EdkDSP firmware. Started debug demo - linux target t01_l42                                                                                                                                                                                                                                                                                          |

| Figure 25: Select MicroBlaze project edkdsp_fp12_1x8_I for debug44                                                                                                                                                                                                                                                                                                      |

| Figure 26: Select free run of MicroBlaze project edkdsp_fp12_1x8_I 4                                                                                                                                                                                                                                                                                                    |

| Figure 27: Output from ARM MicroBlaze fort t01_I. Compiled EdkDSP firmware                                                                                                                                                                                                                                                                                              |

| Figure 28: Create BOOT.bin for the t01_s demo 4                                                                                                                                                                                                                                                                                                                         |

| Figure 29: Create BOOT.bin for the t01_I demo                                                                                                                                                                                                                                                                                                                           |

### **Table of Tables**

| Table 1: (8xSIMD) EdkDSP bce_fp12_1x8_40 accelerator vector operations                   |      |

|------------------------------------------------------------------------------------------|------|

| Table 2: PicoBlaze6 ports forming VLIW instruction for the 8xSIMD EdkDSP data flow unit  | . 11 |

| Table 3: PicoBlaze6 precompiled support functions                                        | . 12 |

| Table 4: MicroBlaze access names to 8xSIMD EdkDSP memory banks                           | . 13 |

| Table 5: MicroBlaze WAL error codes                                                      | . 13 |

| Table 6: MicroBlaze API functions for communication with 8xSIMD EdkDSP IP core           | . 13 |

| Table 7: Organisation of DDR3 memory                                                     | . 18 |

| Table 8: Description of ARM SDSoC acceleration examples compatible with 8xSIMD EdkDSP IP |      |

3/54

### 1. EdkDSP IP Core - Introduction

This report describes design of reprogrammable 8xSIMD EdkDSP IP core for the 28nm FDSOI digital designs of the THINGS2DO project. The IP has been designed with support of high level flow and tested on the Zynq all programmable 28nm chip with two Arm A9 processors and programmable logic area.

The developed SW API, algorithmic implementation and mapping to the 8xSIMD EdkDSP IP forms a base for the possible subsequent implementations in the 28nm FDSOI technology.

#### Specification of problem to be solved by the EdkDSP IP Core: Active acoustics noise cancellation for the hands free telephony.

The near end signal e(i) (voice of a speaker) is disturbed by a disturbance signal received by the near end microphone. This unknown disturbance y(i) is generated by a known (measured) far end signal (example: noise from the motor engine) u(i). The objective of the active acoustics noise cancellation is to use the measured disturbed near end microphone signal d(i) and the signal measured by the far end microphone u(i) for reconstruction of the near end speaker signal e(i) with cancelled disturbance.

The transfer function from the far end (known) source of the disturbance is modelled by a recursive FIR filter with 2000 coefficients with sampling rate 90 kHz.

#### **Recursive FIR filter algorithm:**

Objective of FIR filter is to generate sequence of modelled system outputs d(i) based on the sequence of system inputs u(i) and constant vector of N FIR filter coefficients. The generated output sequence includes also the random additive output noise defined by white noise signal e(i).

$\begin{aligned} & x(i) = u(i) \\ & y(i) = [w(1), w(2), ..., w(N)] * [x(i), x(i-1), ... x(i-N+1)]^T \\ & d(i) = y(i) + e(i) \end{aligned}$

#### Recursive adaptive LMS filter algorithm:

Objective of adaptive LMS filter is to identify recursively an unknown vector of N=2000 FIR filter coefficients from a sequence of system inputs u(i) and system outputs d(i) with sampling rate 90 kHz. The algorithm works under an assumption that the measured output sequence d(i) has been generated by a FIR filter with unknown coefficients with dimension N=2000 and includes also the unknown random white noise signal. Signal e(i) is estimated by the adaptive LMS filter.

$\begin{array}{l} x(i) = u(i) \\ y(i) = \left[w(1), w(2), \dots, w(N)\right] * \left[x(i), x(i-1), \dots x(i-N+1)\right]^{\mathsf{T}} \\ e(i) = d[i] - y[i] \\ \left[w(1), w(2), \dots, w(N)\right] = \left[w(1), w(2), \dots, w(N)\right] + mu * e(i) * \left[x(i), x(i-1), \dots x(i-N+1)\right] \end{array}$

Where N is order of the FIR and LMS filter. N = 2000 in the implemented designs.

u(i) is scalar, floating point input to the system

d(i) is scalar, floating point output of a system

y(i) is scalar, floating point output of FIR filter

e(i) is scalar, floating point prediction error

[w(1), w(2), ..., w(N)] is vector of N scalar, floating point FIR filter coefficients, N=2000.

mu is scalar, floating point constant used for control of the speed of convergence of the adaptive LMS filter.

4/54

|        | department of |

|--------|---------------|

| signau | processing    |

|        |               |

http://zs.utia.cas.cz

#### The 8xSIMD EdkDSP IP Core

The 8xSIMD EdkDSP IP Core is configured for accelerated floating point computation of the recursive FIR filter with constant parameters N=2000 and for acceleration of the adaptive recursive LMS filter with N=2000 unknown coefficients with required sustained sampling frequency 90 kHz. The FIR filter models the environment and generates the sequence of u(i), d(i) data measurements. The LMS filter serves for reconstruction of the unknown e(i) sequence – the speaker voice with partially cancelled disturbance from the far distance source.

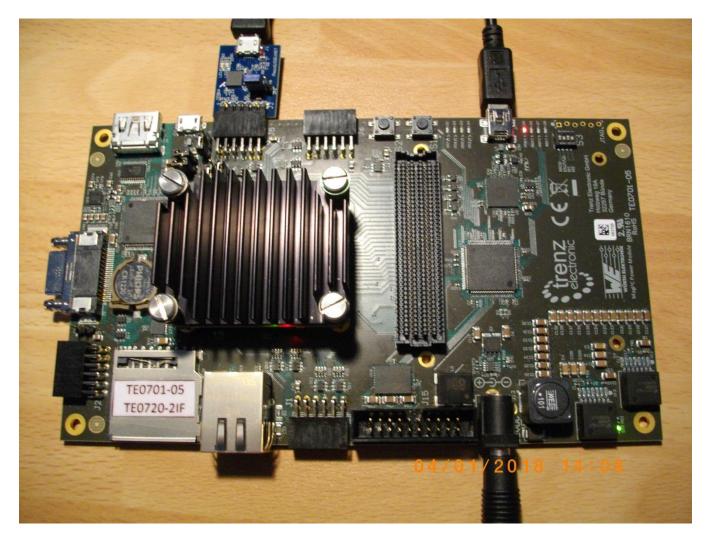

#### **Evaluation system**

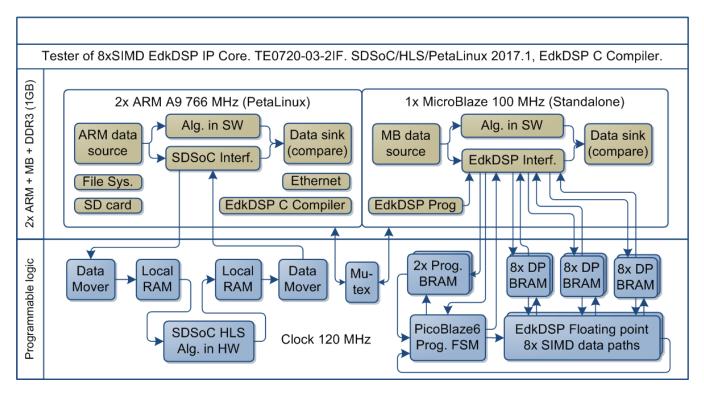

The 8xSIMD EdkDSP IP Core is programmed, evaluated and debugged in HW Xilinx Zynq module TE0720-IF [1]. The 28nm Xilinx Zynq device xc7z020-2I has two 32 bit ARM Cortex A9 processors operating at 766 MHz and single MicroBlaze 32 bit soft core processor operating at 100 MHz.

The Zynq programmable logic area is used for one 8xSIMD EdkDSP IP (operating at 120 MHz) and also for demonstration of compatibility of the EdkDSP IP with examples of Xilinx SDSoC 2017.1 HW accelerators.

The EdkDSP IP Core is 8xSIMD floating point accelerator. It is reprogrammable in runtime by change of firmware of a PicoBlaze6 8bit controller. The PicoBlaze6 controller schedules vector operations performed in the 8xSIMD floating point data paths. The PicoBlaze6 controller serves as re-programmable finite state machine (FSM). It is programmed by firmware compiled by an EdkDSP C Compiler and Assembler. The EdkDSP C Compiler and Assembler are implemented as application programs running on the embedded PetaLinux 2017.1 operating system. The 8xSIMD EdkDSP IP is controlled by the 32bit MicroBlaze processor. MicroBlaze runs programs from the DDR3 memory. The DDR3 is interfaced by an Instruction and Data cache (32k x 32bit) with HPO AXI interface.

The 8xSIMD EdkDSP IP is connected to the MicroBlaze by local dual-ported memories. MicroBlaze implements data communication from DDR3 to 8xSIMD EdkDSP dual-ported memories in software. This communication is performed in parallel with the 8xSIMD parallel floating point computation in the 8xSIMD EdkDSP IP.

| Parameter                              | Requirement | SW MicroBlaze 100 MHz | 8xSIMD EdkDSP 120 MHz |

|----------------------------------------|-------------|-----------------------|-----------------------|

| FIR filter sampling rate Order N=2000  | 90 kHz      | 2.5 kHz (NO)          | 288 kHz (YES)         |

| FIR sustained performance (MFLOPs)     | 360 MFLOPs  | 10 MFLOPs (NO)        | 1152 MFLOPs (YES)     |

| LMS filter sampling rate Order N=2000  | 90 kHz      | 1.25 kHz (NO)         | 92 KHz (YES)          |

| LMS sustained performance (MFLOPs)     | 720 MFLOPs  | 10 MFLOPs (NO)        | 738 MFLOPs (YES)      |

| Bit exact identical results for 8xSIMD | Required    | YES                   | YES                   |

| EdkDSP IP and MB (FIR and LMS)         |             |                       |                       |

| Parallel EdkDSP computation and data   | Required    | YES                   | YES                   |

| transfers to/from DDR3 by MB           |             |                       |                       |

| Runtime change of 8xSIMD EdkDSP IP     | Required    | NA                    | YES                   |

| Embedded 8xSIMD EdkDSP C compiler      | Required    | NA                    | YES                   |

| Compatibility with SDSoC 2017.1        | Required    | YES                   | YES                   |

| Compatibility with PetaLinux 2017.1    | Required    | YES kHz               | YES                   |

| Compatibility with free SDK 2017.1     | Required    | YES                   | YES                   |

| and free edition of Vivado HLS 2017.1  |             |                       |                       |

5/54

#### Main reached results for FIR & LMS filter implementation on the 8xSIMD EdkDSP IP on TE0720-2I module:

#### **Conclusion:**

The required LMS filter sampling rate 90 KHz (with N=2000) was reached. The maximum is 92 kHz for the adaptive LMS filter and 288 kHz for the FIR filter.

### 2. EdkDSP IP Core – Implementation Details

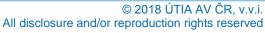

Figure 1: Tester of 8xSIMD EdkDSP floating point accelerator IP core.

#### Parameters of the 8xSIMD EdkDSP IP core

8x SIMD EdkDSP floating point accelerator IP core supports 8xSIMD vector floating point operations performed from/to dual-ported BRAMs A, B, Z. Each dual-ported BRAM has 8 parallel layers of 1024 32bit words. The set of supported floating point operations is different for different grades [10|20|30|40] of the 8xSIMD EdkDSP accelerator IPs. The supported floating point operations are summarised in *Table 1*.

The accelerator **bce\_fp12\_1x8\_0\_axiw\_v1\_10** is area **optimized** and supports only data transfers and vector floating point operations FPADD, FPSUB in 8 SIMD data paths.

The accelerator **bce\_fp12\_1x8\_0\_axiw\_v1\_20** performs identical operations as bce\_fp12\_1x8\_0\_axiw\_v1\_10 plus the vector floating point MAC operations in 8 SIMD data paths. MAC is supported for length of vectors 1 up to 10. This accelerator is optimized for applications like floating point matrix multiplication with one row and column dimensions <= 10.

The accelerator **bce\_fp12\_1x8\_0\_axiw\_v1\_30** supports identical operations as bce\_fp12\_1x8\_0\_axiw\_v1\_20 plus HW-accelerated computation of the floating point vector-by-vector dot-product operators performed in 8 SIMD data paths. It is optimized for parallel computation of up to 8 FIR or LMS filters, each with size up to 250 coefficients. It is also efficient in case of floating point matrix by matrix multiplications, where one of the dimensions is large (in the range from 11 to 250).

The accelerator **bce\_fp12\_1x8\_0\_axiw\_v1\_40** supports identical operations as bce\_fp12\_1x8\_0\_axiw\_v1\_30 plus an additional HW support of dot product. It is computed in 8 data paths with HW-supported wind-up into single scalar result propagated into all SIMD planes.

6/54

signal processing

http://zs.utia.cas.cz

All **bce\_fp12\_1x8\_0\_axiw\_v1\_[10|20|30|40]** accelerators support single data path for pipelined, floating-point division operations with vector operands taken from the first SIMD plain and the result is propagated into all 8 SIMD plains.

All **bce\_fp12\_1x8\_0\_axiw\_v1\_[10|20|30|40]** accelerators are suitable for applications like adaptive normalised LMS and NLMS filters and square root free versions of adaptive RLS QR filters and adaptive RLS LATTICE filters.

| Name in MicroBlaze C value (dec) |      | 8xSIMD Floating point Operation                                                                       |  |  |

|----------------------------------|------|-------------------------------------------------------------------------------------------------------|--|--|

| WAL_BCE_JK_VVER                  | = 0  | Return capabilities of the (8xSIMD) EdkDSP accelerator                                                |  |  |

| WAL_BCE_JK_VZ2A                  | = 1  | 8xSIMD copy a <sub>m</sub> [i] <= z <sub>m</sub> [j]; m=18 IP core: 10,20,30,40                       |  |  |

| WAL_BCE_JK_VB2A                  | = 2  | 8xSIMD copy a <sub>m</sub> [i] <= b <sub>m</sub> [j]; m=18 IP core: 10,20,30,40                       |  |  |

| WAL_BCE_JK_VZ2B                  | = 3  | 8xSIMD copy b <sub>m</sub> [i] <= z <sub>m</sub> [j]; m=18 IP core: 10,20,30,40                       |  |  |

| WAL_BCE_JK_VA2B                  | = 4  | 8xSIMD copy b <sub>m</sub> [i] <= a <sub>m</sub> [j]; m=18 IP core: 10,20,30,40                       |  |  |

|                                  |      |                                                                                                       |  |  |

| WAL_BCE_JK_VADD                  | = 5  | 8xSIMD add z <sub>m</sub> [i] <= a <sub>m</sub> [j] + b <sub>m</sub> [k] ]; m=18 IP core: 10,20,30,40 |  |  |

| WAL_BCE_JK_VADD_BZ2A             | = 6  | 8xSIMD add a <sub>m</sub> [i] <= b <sub>m</sub> [j] + z <sub>m</sub> [k] ]; m=18 IP core: 10,20,30,40 |  |  |

| WAL_BCE_JK_VADD_AZ2B             | = 7  | 8xSIMD add b <sub>m</sub> [i] <= a <sub>m</sub> [j] + z <sub>m</sub> [k] ]; m=18 IP core: 10,20,30,40 |  |  |

|                                  |      |                                                                                                       |  |  |

| WAL_BCE_JK_VSUB                  | = 8  | 8xSIMD sub z <sub>m</sub> [i] <= a <sub>m</sub> [j] - b <sub>m</sub> [k]; m=18 IP core: 10,20,30,40   |  |  |

| WAL_BCE_JK_VSUB_BZ2A             | = 9  | 8xSIMD sub a <sub>m</sub> [i] <= b <sub>m</sub> [j] - z <sub>m</sub> [k]; m=18 IP core: 10,20,30,40   |  |  |

| WAL_BCE_JK_VSUB_AZ2B             | = 10 | 8xSIMD sub b <sub>m</sub> [i] <= a <sub>m</sub> [j] - z <sub>m</sub> [k]; m=18 IP core: 10,20,30,40   |  |  |

|                                  |      |                                                                                                       |  |  |

| WAL_BCE_JK_VMULT                 | = 11 | 8xSIMD mult z <sub>m</sub> [i] <= a <sub>m</sub> [j] * b <sub>m</sub> [k]; m=18 IP core: 10,20,30,40  |  |  |

| WAL_BCE_JK_VMULT_BZ2A            | = 12 | 8xSIMD mult a <sub>m</sub> [i] <= b <sub>m</sub> [j] * z <sub>m</sub> [k]; m=18 IP core: 10,20,30,40  |  |  |

| WAL_BCE_JK_VMULT_AZ2B            | = 13 | 8xSIMD mult b <sub>m</sub> [i] <= a <sub>m</sub> [j] * z <sub>m</sub> [k]; m=18 IP core: 10,20,30,40  |  |  |

|                                  |      |                                                                                                       |  |  |

| WAL_BCE_JK_VPROD                 | = 14 | 8xSIMD vector products: IP core: 30,40                                                                |  |  |

|                                  |      | z <sub>m</sub> [i] <= a <sub>m</sub> '[jj+nn]*b <sub>m</sub> [kk+nn]; m=18; nn range 1255             |  |  |

|                                  |      |                                                                                                       |  |  |

| WAL_BCE_JK_VMAC                  | = 15 | 8xSIMD vector MACs: IP core: 20,30,40                                                                 |  |  |

|                                  |      | z <sub>m</sub> [ii+nn] <= z <sub>m</sub> [ii+nn] + a <sub>m</sub> [jj+nn] * b <sub>m</sub> [kjk+nn];  |  |  |

|                                  |      | nn range 113                                                                                          |  |  |

| WAL_BCE_JK_VMSUBAC               | = 16 | 8xSIMD vector MSUBACs IP core: 20,30,40                                                               |  |  |

|                                  |      | z <sub>m</sub> [ii+nn] <= z <sub>m</sub> [ii+nn] - a <sub>m</sub> [jj+nn] * b <sub>m</sub> [kjk+nn];  |  |  |

|                                  |      | nn range 113                                                                                          |  |  |

| WAL_BCE_JK_VPROD_S8              | = 17 | 8xSIMD vector product (extended) IP core: 40                                                          |  |  |

|                                  |      | $z_m[i] \le ( (a_1'[jj+nn]*b_1[kk+nn]+a_2'[jj+nn]*b_2[kk+nn])$                                        |  |  |

|                                  |      | + (a <sub>3</sub> '[jj+nn]*b <sub>3</sub> [kk+nn]+a <sub>4</sub> '[jj+nn]*b <sub>4</sub> [kk+nn]) )   |  |  |

|                                  |      | +                                                                                                     |  |  |

|                                  |      | ( (a <sub>5</sub> '[jj+nn]*b <sub>5</sub> [kk+nn]+a <sub>6</sub> '[jj+nn]*b <sub>6</sub> [kk+nn])     |  |  |

|                                  |      | + (a <sub>7</sub> '[jj+nn]*b <sub>7</sub> [kk+nn]+a <sub>8</sub> '[jj+nn]*b <sub>8</sub> [kk+nn]) );  |  |  |

|                                  |      | m=18; nn range 1255                                                                                   |  |  |

| WAL_BCE_JK_VDIV                  | = 20 | vector division (extended) IP core: 10,20,30,40                                                       |  |  |

|                                  |      | $z_m[i] \le a_1[j] / b_1[k]; m=18$                                                                    |  |  |

Table 1: (8xSIMD) EdkDSP bce\_fp12\_1x8\_40 accelerator vector operations.

http://zs.utia.cas.cz

7/54

#### Ports of the 8xSIMD EdkDSP accelerator

•

•

- bce\_atoa[0:9] Memory A address (addressing 1024 32 bit floating point values)

- bce\_atob[0:9] Memory B address (addressing 1024 32 bit floating point values)

- bce\_atoz[0:9] Memory Z address (addressing 1024 32 bit floating point values)

- bce\_done[0:7] Vector operation in progress or finished

- bce\_led4b[0:3] 4 bit output, intended for led signalling. (Unconnected in the evaluation design).

- bce\_mode[0:3] Mode of the communication protocol PicoBlaze6 MicroBlaze

- bce\_op[0:7] Vector operation to be performed.

- bce\_port[0:7] 8 bit output port. (Unconnected in the evaluation design).

- bce\_port\_id[0:7] 8 bit output External port address.

Address space [0x0 ... 0x1F] is reserved for optimized construction of the VLIW instruction to the 8xSIMD vector processing unit of the EdkDSP. Address space [0x20 ... 0xFF] can be used by the user.

- bce\_port\_wr 1 bit output. Write strobe for write of 8 bit data to the external port address.

- bce\_r\_pb 1 bit output. Reset of the PicoBlaze6.

- bce\_we 1 bit output. Write strobe signals start of execution of a VLIW instruction by the 8xSIMD vector processing unit of the EdkDSP.

- bce\_dip4b[0:3] 4bit input (Connected to a constant in the evaluation design).

- Bce\_gpi8b[0:7] 8bit input (Connected to a constant in the evaluation design).

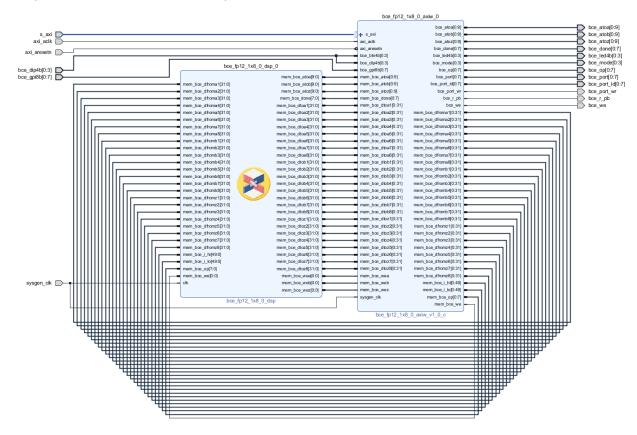

Figure 2: 8xSIMD EdkDSP floating point accelerator IP core.

#### Interface of the 8xSIMD EdkDSP IP to the MicroBlaze processor

The EdkDSP IP core is connected to the 100 MHz MicroBlaze processor via the 100 MHz 32bit AXI lite bus represented by port **s\_axi**, 100 MHz clock input **axi\_aclk** and an asynchronous reset signal **axi\_aresetn**. See *Figure 2*.

The debug ports are used for the real-time visualisation, debug and analysis of the computation implemented inside of the 8xSIMD data flow unit (DFU) of the (8xSIMD) EdkDSP accelerator IP. This makes easier to debug the compiled PicoBlaze6 firmware code. The implemented in circuit logic analyser (ILA) debug probes can capture 8096 data samples and provide visibility for the auto-generated addresses and for the detailed schedule of vector operation in the 8xSIMD EdkDSP IP core. See *Figure 2*.

*Figure* 3 presents connection of the two parts of the 8xSIMD EdkDSP IP core.

Figure 3: Internal details of (8xSIMD) EdkDSP floating point accelerator IP core.

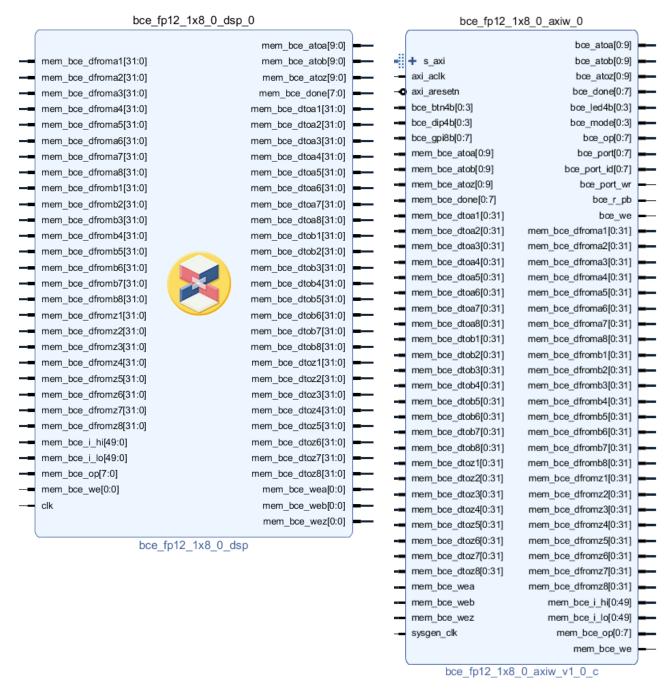

*Figure 4* presents ports of the Edk IP and the DSP IP part of the 8xSIMD EdkDSP IP core. All bce\_fp12\_1x8\_0\_axiw\_v1\_[10|20|30|40] accelerators versions have identical Edk IP part.

The DSP part has identical ports and connectivity (see

*Figure* 3) for all bce\_fp12\_1x8\_0\_axiw\_v1\_[10|20|30|40] accelerators versions.

ŪTĬA

http://zs.utia.cas.cz

Figure 4: (8xSIMD) Edk part and DSP part of the EdkDSP floating point accelerator IP core.

The Edk part of the EdkDSP floating point accelerator IP core **bce\_fp12\_1x8\_0\_axiw\_v1\_0\_c** includes inside the PicoBlaze6 controller, its program memories P0 and P1 and the 8xSIMD dual-ported block-ram memories 8xA, 8xB and 8xZ designed for parallel access. The **bce\_fp12\_1x8\_0\_axiw\_v1\_0\_c** IP is designed in the Xilinx System Generator 14.5 and ported to the Vivado 2017.1 compatible IP core. The PicoBlaze6 firmware executes C code and supports C constructs like loops, while, if, else, function calls etc.

The first of the two ports of all block-rams are accessed by the MicroBlaze as memory via the Axi-lite bus.

The second of the two ports of both program memories P0 and P1 are connected to the PicoBlaze6 controller.

• The second of the two ports of all data memories 8xA, 8xB and 8xZ are connected to the floating point data paths of the data flow unit (DFU) unit and support parallel access.

The DFU **bce\_fp12\_1x8\_0\_dsp** is designed in the Xilinx System Generator for DSP 2017.1. It contains 8 pipelined floating point ADD units, 8 pipelined floating point MULT units and one pipelined floating point DIV unit. The DFU supports all vector operations defined in *Table 1*.

- The 100bit VLIW instruction is transferred in two 50bit ports **mem\_bce\_i\_lo** and **mem\_bce\_i\_hi**. The VLIW instruction is set by dedicated PicoBlaze6 output ports. See *Table 2*.

- The 8xSIMD data flow unit executes 8xSIMD floating point operations defined in *Table 1*.

- The concrete 8xSIMD operation is defined by the PicoBlaze6 DFU\_OP 8bit output register driving the mem\_bce\_op port of the bce\_fp12\_1x8\_0\_axiw\_v1\_0\_c IP. The transfer of the complete VLIW instruction (100+8 bits) is triggered by the write strobe signal mem\_bce\_we. It is activated by PicoBlaze6 program write of the 8xSIMD operation DFU\_OP. See *Table 2*.

The 8xSIMD data flow unit (DFU) indicates end of the operation in the 8bit output port **mem\_bce\_done**. PicoBlaze6 program can execute few instructions in parallel to the 8xSIMD operation defined in DFU\_OP. End of the 8xSIMD operation is detected by the PicoBlaze6 program by reading of the input 8bit port **mem\_bce\_done**.

PicoBlaze6 firmware defines the sequence of VLIW instructions for the 8xSIMD DFU unit by its dedicated output registers. PicoBlaze6 addresses of these dedicated output registers are listed in *Table 2*.

| Format      | VLIW                                                                                                                                                                                                        | Description of sections defined in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [msblsb]    | [2x 50bit]                                                                                                                                                                                                  | VLIW instruction for the EdkDSP Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             | mem_bce_i_hi                                                                                                                                                                                                | Flow Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | mem_bce_i_lo                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [2bit,8bit] | 10 bit [4940]                                                                                                                                                                                               | Number of 8xSIMD steps (0 255)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| [2bit,8bit] | 10 bit [3930]                                                                                                                                                                                               | Auto increment of Z address (0 255)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [2bit,8bit] | 10 bit [2920]                                                                                                                                                                                               | Set Z address after auto incr overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2bit,8bit] | 10 bit [1910]                                                                                                                                                                                               | Initial Z address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| [2bit,8bit] | 10 bit [0900]                                                                                                                                                                                               | Auto increment of B address (0 255)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [2bit,8bit] | 10 bit [4940]                                                                                                                                                                                               | Set B address after auto incr overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2bit,8bit] | 10 bit [3920]                                                                                                                                                                                               | Initial B address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| [2bit,8bit] | 10 bit [2920]                                                                                                                                                                                               | Auto increment of A address (0 255)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [2bit,8bit] | 10 bit [1910]                                                                                                                                                                                               | Set A address after auto incr overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [2bit,8bit] | 10 bit [0900]                                                                                                                                                                                               | Initial A address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [4bit,4bit] | 8 bit                                                                                                                                                                                                       | Set actual VLIW instr. memory (0 15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [8bit]      | 8 bit                                                                                                                                                                                                       | Execute SIMD operation with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                                                                                                                                                                                                             | parameters in the actual VLIW instr.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                                                                                                                                                                                                             | memory (set by the PBP_REG01 port).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | [msblsb]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit]<br>[2bit,8bit] | [msblsb]       [2x 50bit]         mem_bce_i_lo         [2bit,8bit]       10 bit [4940]         [2bit,8bit]       10 bit [3930]         [2bit,8bit]       10 bit [2920]         [2bit,8bit]       10 bit [1910]         [2bit,8bit]       10 bit [1910]         [2bit,8bit]       10 bit [4940]         [2bit,8bit]       10 bit [1910]         [2bit,8bit]       10 bit [4940]         [2bit,8bit]       10 bit [2920]         [2bit,8bit]       10 bit [2920]         [2bit,8bit]       10 bit [1910]         [2bit,8bit]       10 bit [1910]         [2bit,8bit]       10 bit [0900]         [4bit,4bit]       8 bit |

11/54

Table 2: PicoBlaze6 ports forming VLIW instruction for the 8xSIMD EdkDSP data flow unit.

http://zs.utia.cas.cz

ŪTIA

### 3. EdkDSP IP Core – PicoBlaze6 C Application Interface Functions

The EdkDSP compiler embedded compilation of simple C and ASM programs or the PicoBlaze6 controller. PicoBlaze6 programs can use predefined and precompiled library functions listed in *Table 3*. Functions are optimized in the PicoBlaze6 assembler code, and occupy fixed area of the firmware and serve as common simple API for C and ASM PicoBlaze6 programs.

PicoBlaze6 firmware image with precompiled support functions is present in MicroBlaze header file **fill\_def\_program\_store.h** PicoBlaze6 application program firmware is merged with this precompiled image by the MicroBlaze SW program.

| PicoBlaze6 predefined functions                                 | Description                                                                     |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------|

| unsigned char mb2pb_read_data();                                | Single unsigned char from MicroBlaze to PicoBlaze6                              |

| void pb2mb_write(unsigned char data);                           | Single unsigned char from PicoBlaze6 to MicroBlaze                              |

| void pb2mb_eoc(unsigned char data);                             | EOC unsigned char from PicoBlaze6 to MicroBlaze                                 |

| void pb2mb_req_reset(unsigned char data);                       | Request from PicoBlaze6 to MicroBlaze to initiate PB reset                      |

| void pb2mb_reset();                                             | Information from PicoBlaze6 to MicroBlaze - PB reset                            |

| void pb2dfu_set(unsigned char mem,                              | Set one section of the VLIW instruction for the data flow unit                  |

| unsigned char data);                                            | (DFU) to an unsigned char data. VLIW instruction sections are                   |

|                                                                 | addressed as PicoBlaze6 8bit output ports defined in Table 2                    |

| void pb2dfu_wait4hw();                                          | PicoBlaze6 function is waiting for the termination of data flow unit operation. |

| unsigned char led2pb();                                         | Write from PicoBlaze6 to 4 bit led output port                                  |

| unsigned char btn2pb();                                         | Read from 4 bit input port to PicoBlaze6                                        |

| unsigned char hex_h(unsigned char ch);                          | Translate upper 4 bit nibble of an unsigned char to ascii                       |

| unsigned char hex_l(unsigned char ch);                          | Translate lower 4 bit nibble of an unsigned char to ascii                       |

| void pb2lcd_ascii_char(unsigned char ch,<br>unsigned char pos); | Write from PicoBlaze6 to LCD asci alphanumerical display                        |

12/54

http://zs.utia.cas.cz

### 4. EdkDSP IP Core – MicroBlaze C Application Interface Functions

MicroBlaze program is responsible for data communication, programming and initialization of the PicoBlaze6 and global scheduling of the implemented algorithm. The API providing MicroBlaze - Picoblaze6 interface is called Worker Abstraction Layer (WAL).

- 8xSIMD EdkDSP memory pointers and program memory pointers (from MicroBlaze view) are defined in *Table 4*.

- WAL error codes are defined in *Table 5*.

- 8xSIMD EdkDSP is supported by API functions collected in the WAL API are listed and described in *Table* 6.

| MicroBlaze access names | Description of the 8xSIMD EdkDSP memory banks                      |

|-------------------------|--------------------------------------------------------------------|

| WAL_BCE_JK_DMEM_A       | index of the A data memory banks (8x [01023] 32bit words)          |

| WAL_BCE_JK_DMEM_B       | index of the B data memory banks (8x [01023] 32bit words)          |

| WAL_BCE_JK_DMEM_Z       | index of the Z data memory banks (8x [01023] 32bit words)          |

|                         |                                                                    |

| WAL_CMEM_MB2PB          | index to MB2PB control memory (the control register of the worker) |

| WAL_CMEM_PB2MB          | index to PB2MB control memory (the status register of the worker)  |

| WAL_PBID_P0             | index to PO control memory (PicoBlaze program memory 1)            |

| WAL_PBID_P1             | index to P1 control memory (PicoBlaze program memory 2)            |

#### Table 4: MicroBlaze access names to 8xSIMD EdkDSP memory banks

#### Table 5: MicroBlaze WAL error codes

| MicroBlaze WAL codes | Value | Description                 |

|----------------------|-------|-----------------------------|

| WAL_RES_OK           | 0     | all is OK                   |

| WAL_RES_WNULL        | 1     | argument is a NULL          |

| WAL_RES_ERR          | -1    | generic error               |

| WAL_RES_ENOINIT      | -2    | not initiated               |

| WAL_RES_ENULL        | -3    | null pointer                |

| WAL_RES_ERUNNING     | -4    | worker is running           |

| WAL_RES_ERANGE       | -5    | index/value is out of range |

Table 6: MicroBlaze API functions for communication with 8xSIMD EdkDSP IP core

#### MicroBlaze API functions for communication with 8xSIMD EdkDSP IP core

wal\_init\_worker() - generalised function for worker initialising

**\*wrk** is a pointer to the worker structure.

This function is designed for calling from user application. The function checks if the \*wrk structure is prepared to initiate worker (the family description structure must be set). Then the assigned family function (init\_wrk()) is called. In the called function all arrays of pointers to shared memories should be initiated.

Return Value: The function returns return code WAL\_RES\_OK if successful and WAL\_RES\_E... if any error occurs.

13/54

#### int wal\_init\_worker(struct wal\_worker \*wrk);

signal processing

#### wal\_done\_worker - generalised function for worker clean-up

\*wrk is a pointer to the worker structure

This function is designed for calling from user application. The function calls done function (done\_wrk()) assigned to family description structure. In the called function all dynamically allocated worker structures, memories and resources should be clean-up and released if they have been created in the worker init function.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_done\_worker(struct wal\_worker \*wrk);

#### wal\_reset\_worker() - generalised function for worker hard reset

\*wrk is a pointer to the worker structure

This function is designed for calling from user application. The function calls reset function (reset\_wrk()) assigned to the family description structure. In the called function the worker control registers should be reset (by HARD RESET bit in the worker control register). The reset is not acknowledged by accelerator.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_reset\_worker(struct wal\_worker \*wrk);

wal\_start\_operation() - generalised function for starting operation on the accelerator.

**\*wrk** is a pointer to the worker structure. **\*pbid** is an index of used PB firmware (WAL\_PBID\_...)

This function is designed for calling from user application. The function checks if the accelerator is in the idle state and then it calls function for starting operation (start\_op()) assigned to the family description structure. The called function should start a new accelerator operation by setting accelerator control register and checking status register. This function is blocking, i.e. it waits for acknowledgement from accelerator.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_start\_operation(struct wal\_worker \*wrk, unsigned int pbid);

wal\_end\_operation() - generalised function for finishing operation on the accelerator.

**\*wrk** is a pointer to the worker structure.

This function is designed for calling from user application. The function checks if the accelerator is in processing state and then it calls function for ending operation (end\_op()) assigned to the family description structure. The called function should stop processing operation on the accelerator. And it waits for synchronization with the accelerator, therefore the function is blocking.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_end\_operation(struct wal\_worker \*wrk);

wal\_mb2pb() - generalised function for setting worker control register.

\*wrk is a pointer to the worker structure. data is user data to be send to worker control register.

This function is designed for calling from user application. The function calls function for setting worker control signal processing http://zs.utia.cas.cz

14/54

ŪTĪA

register (mb2pb()) assigned to the family description structure. The called function should send user data through control register with controlling READ bit. It should also waits for synchronization with accelerator.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_mb2pb(struct wal\_worker \*wrk, const uint32\_t data);

wal\_pb2mb() - generalised function for reading worker status register.

**\*wrk** is a pointer to the worker structure. **\*data** is a pointer to an output buffer where read user data is written.

This function is designed for calling from user application. The function calls function for reading worker status register (pb2mb()) assigned to the family description structure. The called function should read user data through worker status register with waiting for synchronization with accelerator.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_pb2mb(struct wal\_worker \*wrk, uint32\_t \*data);

**wal\_mb2cmem()** - generalised function for writing a block of data to any worker control or support memory

**\*wrk** is a pointer to the worker structure. **memid** is an index of control/support memory where data are written to (WAL\_CMEM\_... or WAL\_...\_SMEM\_...). **memoffs** is offset in selected memory (in words not in bytes). **outbuf** is a pointer to memory where data are read from. **len** is a number of words to copy from **outbuf** to accelerator control memory.

This function is designed for calling from user application. The function checks index of the required memory and then it calls function for writing data to any control/support memory (mb2cmem()) assigned to the family description structure. The called function should get a pointer to the right memory according to the required index **memid**. For accessing support memories they have to define indices greater then indices to control memories. Then the called function should copy a block of data from CPU memory **outbuf** to an accelerator control/support memory selected by **memid** and offset in selected memory **memoffs**.

Return Value: The function returns WAL\_RES\_... codes.

**wal\_cmem2mb()** - generalised function for reading a block of data from any worker control or support memory

**\*wrk** is a pointer to the worker structure. **memid** is an index of control/support memory where data are read from

( WAL\_CMEM\_... or WAL\_...\_SMEM\_...). **memoffs** is offset in selected memory (in words not in bytes). **\*inbuf** is a pointer to memory where data are written to. **Ien** is a number of words to copy from accelerator control memory.

This function is designed for calling from user application. The function checks index of the required memory and then it calls function for reading data from any control/support memory (cmem2mb()) assigned to the family description structure. The called function should get a pointer to the right memory according to the required index **memid**. For accessing support memories they have to define indices greater then indices to

signal processing

control memories. Then the called function should copy a block of data from the accelerator control/support memory selected by **memid** and offset in selected memory **memoffs**.

Return Value: The function returns WAL\_RES\_... codes.

#### int wal\_cmem2mb(struct wal\_worker \*wrk, unsigned int memid, unsigned int memoffs, uint32\_t \*inbuf, unsigned int len);

wal\_mb2dmem() - generalised function for writing a block of data to any worker data memory

**\*wrk** is a pointer to the worker structure. **simdid** is an index of SIMD which data memories are indexed. **memid** is an index of control/support memory where data are written to (WAL\_CMEM\_... or WAL\_...\_SMEM\_...). **memoffs** is offset in selected memory (in words not in bytes). **\*outbuf** is a pointer to memory where data are read from. **Ien** is a number of words to copy from **\*outbuf** to accelerator control memory.

This function is designed for calling from user application. The function checks index of the required memory and then it calls function for writing data to any data memory (mb2dmem()) assigned to the family description structure. The called function should get a pointer to the right memory according to the required SIMD **simdid** and memory index **memid**. Then the called function should copy a block of data from CPU memory **\*outbuf** to the accelerator data memory with offset inside the selected memory **memoffs**.

Return Value: The function returns WAL\_RES\_... codes.

#### int wal\_mb2dmem(struct wal\_worker \*wrk, unsigned int simdid, unsigned int memid, unsigned int memoffs, const void \*outbuf, unsigned int len);

wal\_dmem2mb() - generalised function for writing a block of data to any worker data memory

**\*wrk** is a pointer to the worker structure. **simdid** is an index of SIMD which data memories are indexed. **memid** is an index of control/support memory where data are read from (WAL\_CMEM\_... or WAL\_...\_SMEM\_...). **memoffs** is offset in selected memory (in words not in bytes). **\*inbuf** is a pointer to memory where data are written to. **len** is a number of words to copy from accelerator control memory.

This function is designed for calling from user application. The function checks index of the required memory and then it calls function for reading data from any data memory (dmem2mb()) assigned to the family description structure. The called function should get pointer to the right memory according to the required SIMD **simdid** and memory index **memid**. Then the called function should copy a block of data from the accelerator data memory with offset inside the selected memory **memoffs**.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_dmem2mb(struct wal\_worker \*wrk, unsigned int simdid, unsigned int memid, unsigned int memoffs, void \*inbuf, unsigned int len);

wal\_set\_firmware() - generalised function for writing PicoBlaze firmware

**\*wrk** is a pointer to the worker structure. **pbid** is an index of used PB firmware (WAL\_PBID\_...). **\*fwbuf** is a pointer to a firmware in CPU memory. **fwsize** is a size of the firmware in words, it can be a negative value to set full firmware (4096 words).

This function is designed for calling from user application. The function checks if all arguments are correct and then it calls function for writing PB firmware (set\_fw()). The called function should copy firmware from CPU memory **\*fwbuf** to PicoBlaze6 program memory in the accelerator. The PB program memory is selected by the

signal processing

http://zs.utia.cas.cz

16/54

argument **pbid**. The firmware needn't be full 4096 word long. The firmware length (in words) can be set by the argument **fwsize**. If the **fwsize** is a negative value (you can use defined value WAL\_FW\_WHOLE) the function assumes the FW length is 4096 words.

Return Value: The function returns WAL\_RES\_... codes.

#### int wal\_set\_firmware(struct wal\_worker \*wrk, int pbid, const unsigned int \*fwbuf, int fwsize);

#### wal\_bce\_jk\_get\_id() - implementation of the worker get\_id() function for the BCE\_JK families

**\*wrk** is a pointer to the worker structure. **pbid** is an index of used PB firmware (WAL\_PBID\_...). **outval** is a pointer to an output buffer for read worker ID.

The function emulates reading worker ID from hardware because the BCE\_JK families don't support this operation in the hardware.

Return Value: The function always returns WAL\_RES\_OK.

int wal\_get\_id(struct wal\_worker \*wrk, int pbid, unsigned int \*outval);

wal\_bce\_jk\_get\_cap() - implementation of the worker get\_cap() function for the BCE\_JK families

\*wrk is a pointer to the worker structure. pbid is an index of used PB firmware ( WAL\_PBID\_...). \*outval is a

pointer to an output buffer for read capabilities.

The function sends operation WAL\_BCE\_JK\_VVER to accelerator, reads the worker capabilities and returns the read value in the **\*outval** buffer.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_get\_capabilities(struct wal\_worker \*wrk, int pbid, unsigned int \*outval);

wal\_bce\_jk\_get\_lic() - implementation of the get\_lic() function for the BCE\_JK families

**\*wrk** is a pointer to the worker structure. **pbid** is an index of used PB firmware (WAL\_PBID\_...). **\*outval** is a pointer to an output buffer for read license.

The function reads the license from the worker. For BCE\_JK families the license is a 2bit license down-counter contained in the value returned by accelerator operation WAL\_BCE\_JK\_VVER. The 2bit license counter is returned in the **\*outval** buffer.

Return Value: The function returns WAL\_RES\_... codes.

int wal\_get\_license(struct wal\_worker \*wrk, int pbid, unsigned int \*outval);

All worker abstraction layer API functions listed in *Table 6* are precompiled into the MicroBlaze library **wal.a** and declared in MicroBlaze header files wal.h and **wal\_bce\_jk.h**.

The worker abstraction layer API functions listed in *Table 6* support instantiation of several (more than 1) instances of the 8xSIMD EdkDSP IP core.

17/54

http://zs.utia.cas.cz

### 5. EdkDSP IP Core – Integration with dual core ARM A9 Linux

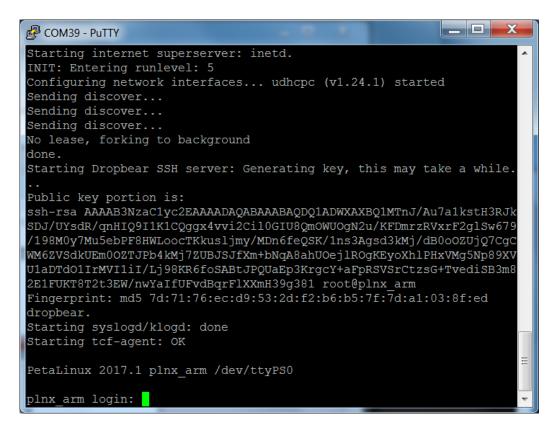

The 8xSIMD EdkDSP IP core is integrated in a tester system with architecture presented in *Figure 1* and photo of the HW presented by *Figure 5* and *Figure 6*.

The dual core ARM Cortex A9 system runs configured PetaLinux 2017.1 operating system and supports:

- Ethernet 1 Gbit

- SSH, telnet, FTP, ...

- The system image is located on SD card. After the initial boot, the file system is decompressed to the RAM FS in DDR3. The SD card file system is mounted and visible in the running Petalinux.

- Symmetrical multiprocessing on two ARM A9 processors

- SDSoC 2017.1 generated HW accelerators with data movers based on:

- Simple DMA with HW supported data movers (DMA data width 32bit or 64bit) with no ARM interrupts. Simple DMA requires allocation of continuous memory space.

- SG DMA with data movers (DMA data width 32bit or 64bit) with ARM interrupts. SG DMA can work with continuous allocation of memory or with standard Linux allocation of memory, where the continuous allocation is not guaranteed.

- HW data movers connected to the advanced cache coherent port resolving in HW the cache coherency of dual core ARM access and data mover access to DDR3.

The MicroBlaze processor and the 8xSIMD EdkDSP IP core require initialisation and synchronisation with Linux and the dual core ARM subsystem. This is arranged by the following configuration of reserved DDR3 memory (1 GB)

| Memory Area (in Bytes)  | Size       | Description                                              |  |

|-------------------------|------------|----------------------------------------------------------|--|

| 0x0000 0000 0x27FF FFFF | 640 M Byte | Memory managed by standard Linux memory allocation       |  |

|                         |            | mechanism. Used by dual core Arm A9 symmetrical          |  |

|                         |            | multiprocessing 32 bit Linux                             |  |

| 0x2800 0000 0x280F FFFF | 1 M Byte   | Reserved for MicroBlaze – ARM communication              |  |

|                         |            | It is continuous memory reserved in Linux configuration  |  |

| 0x2800 0000 0x2810 0FFF | 4 kByte    | Reserved for PicoBlaze6 f0 firmware (MicoBlaze and ARM)  |  |

| 0x2800 1000 0x2810 1FFF | 4 kByte    | Reserved for PicoBlaze6 f1 firmware (MicoBlaze and ARM)  |  |

| 0x2800 2000 0x2810 2FFF | 4 kByte    | Reserved for PicoBlaze6 f2 firmware (MicoBlaze and ARM)  |  |

| 0x2800 3000 0x2810 3FFF | 4 kByte    | Reserved for PicoBlaze6 f3 firmware (MicoBlaze and ARM)  |  |

| 0x2800 4000 0x281F FFFF | Reserved   | Reserved for 8xSIMD EdkDSP data (MicoBlaze and ARM)      |  |

| 0x2810 0000 0x29FF FFFF | 15 M Byte  | MicroBlaze program & data. Microblaze processor IP is    |  |

|                         |            | configured for execution of its code from 0x28100000.    |  |

|                         |            | It is a part of the continuous memory reserved in Linux. |  |

| 0x2A00 0000 0x2FFF FFFF | 112 M Byte | Continuous memory reserved for video frame buffers.      |  |

| 0x3000 0000 0x3FFF FFFF | 256 M Byte | Memory reserved for SDSoC data mover and DMA drivers.    |  |

Table 7: Organisation of DDR3 memory

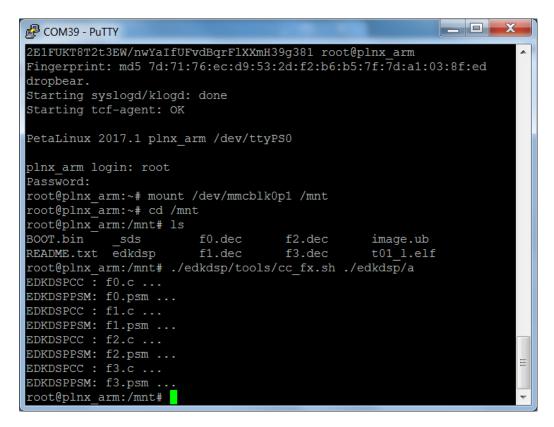

Linux user application uses the four reserved 4k Byte areas for copy of four PicoBlaze6 firmware programs. These programs can be compiled on the dual core ARM A9 from the C and ASM source codes stored as asci files on the mounted SD card file system. Compiled firmware programs are read by the user application running on ARM from the SD card files and copied as data to the reserved 4kB continuous memory areas. MicroBlaze6 program (after HW mutex based synchronisation) reads this data and uses them for programming of PicoBlaze6 FSM of the 8xSIMD EdkDSP IP.

18/54

signal processing

### 6. Setup of Hardware

HW setup is based on commercially accessible components [1], [2], [3], [4]:

TE0720-2IF; Part: XC7Z020-2CLG484I; 1 GByte DDR; Industrial Grade (-40°C to +85°C) [1].

Heatsink for TE0720, spring-loaded embedded [2].

TE0701 Carrier Board for Trenz Electronic 7 Series [3]

Pmod USBUART Serial converter & interface [4].

See the technical reference manuals (TRM) for the description of the TE0720-02-2IF or TE0720-03-2IF module revision [1] and TE0701-04, TE0701-05 or TE0701-06 revision of carrier boards [3].

Figure 5: TE701 carrier board with TE0720-2IF Zynq module

Set the TE0701-06 carrier board switches and jumpers for the TE0720-03-2IF module as follows:

Set switch S3 TE701-04 switch S3: 1=ON 2=OFF 3=ON 4=OFF TE701-05 switch S3: 1=ON 2=OFF 3=ON 4=OFF TE701-06 switch S3: 1=ON 2=OFF 3=ON 4=OFF

19/54

http://zs.utia.cas.cz

- Set jumpers to generate FMC\_VADJ=2.5V TE701-04: (VIOTA=2.5V VIOTB=FMC\_VADJ=VADJ=2.5V) J17: connect 2-3; J21: connect 2-3 TE701-05: (VIOTA=2.5V VIOTB=FMC\_VADJ=VADJ=2.5V) J17: connect 2-3; J21: connect 2-3 TE701-06: (VIOTA=VIOTB=FMC\_VADJ=VADJ=2.5V) J16: closed; J17: open; J21: connect 2-3

- Set switch S4 (only in case of TE701-06) TE701-06 switch S4: (set FMC\_VADJ=2.5V as power source): 1=OFF 2=ON 3=ON 4=OFF

The TE0720-2IF Zynq device works with all IO-bank supply-voltages 2.5V. It is highly recommended to set switches of the TE0701 carrier board and measure the PL IO-bank supply-voltage before mounting of the module on TE0701. See locations and switch positions in the TE0701 TRMs [3].

The USBUART pmod is connected to pins [7 ... 12] of connector J5. Pin 11 is ground. The jumper on the USBUART pmod is set to the default: connect lcl-vcc. The convertor chip is powered from the 5V USB from the PC and generates the local 3.3V for the pmod. See *Figure 5*.

The USBUART pmod providing serial terminal for MicroBlaze is connected to the PC by a Micro USB cable. The TE0701 board ARM serial terminal/JTAG (connector J7) is connected to the PC by a Mini USB (type B) cable. See *Figure 6*.

Figure 6: MiniUSB cable and MicroUSB cable for the Pmod USBUART

http://zs.utia.cas.cz

20/54

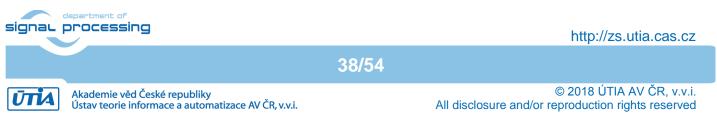

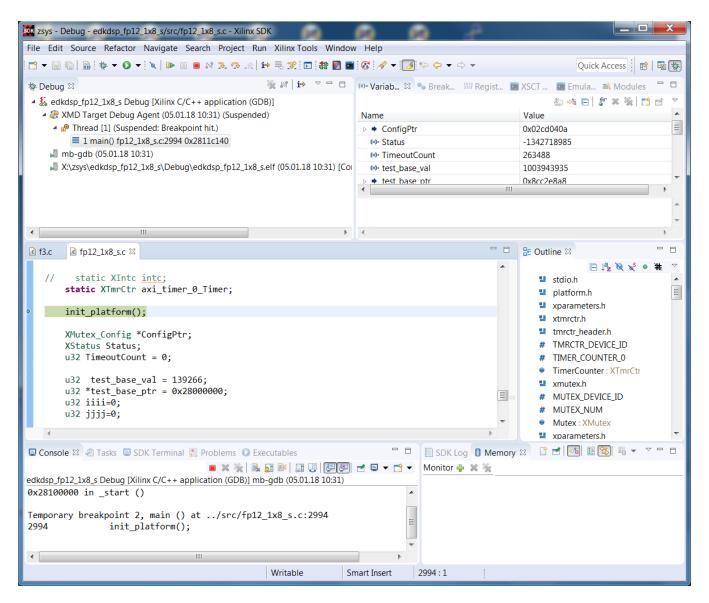

## 7. Installation and Use of Base Evaluation Package

This chapter describes the installation and use of a base evaluation package. Package is demonstrating:

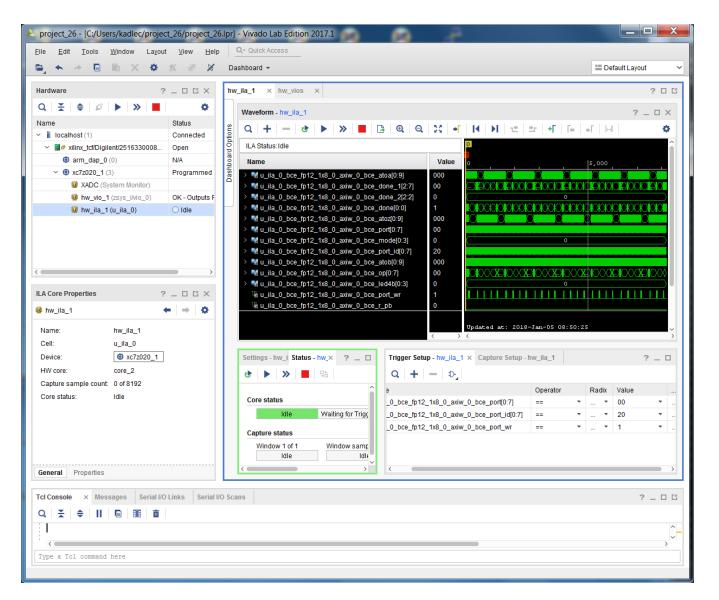

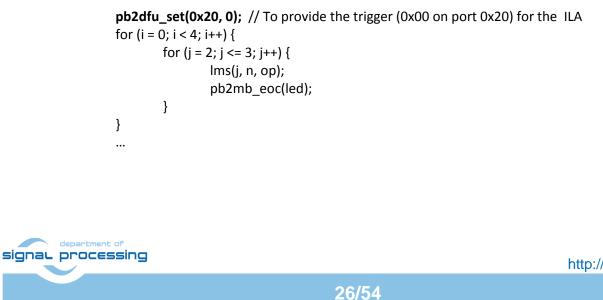

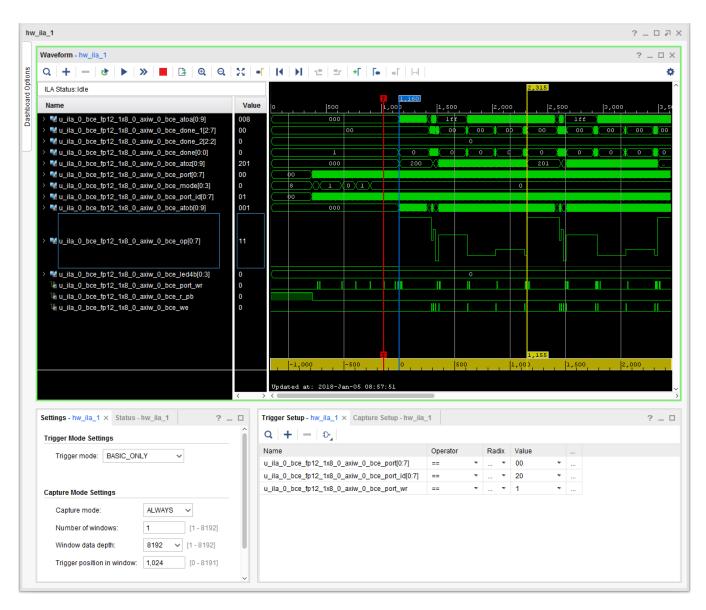

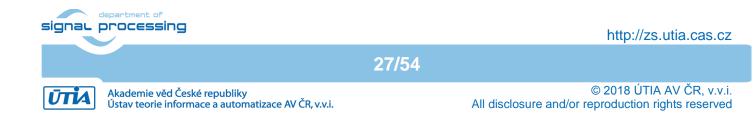

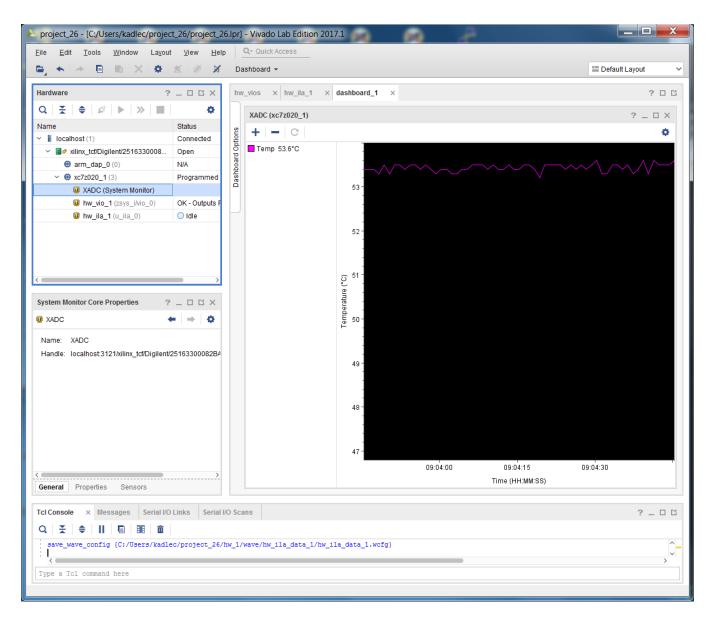

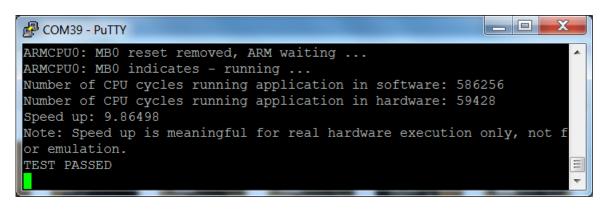

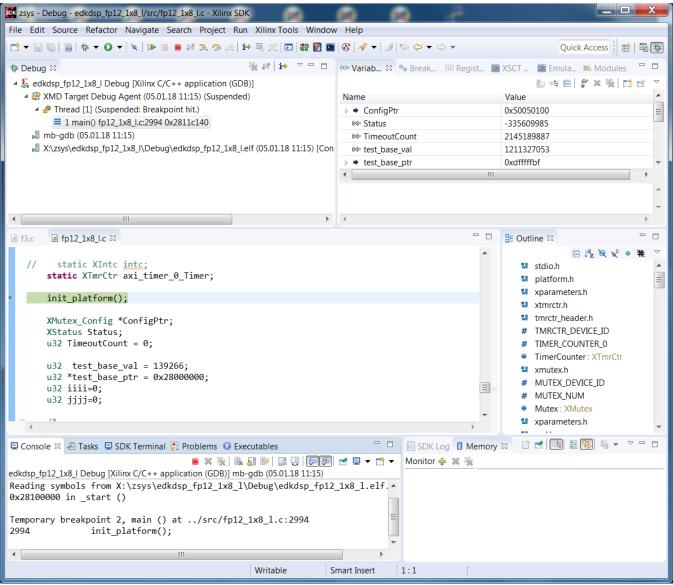

- In-circuit Logic Analyser (ILA) JTAG based inspection/observation/debug of the 8xSIMD EdkDSP IP. ILA works with internal buffer for 8k samples and operates at 120 MHz. See *Figure 8, Figure 9, Figure 10, Figure 11*.

- The standalone examples support ILA and additionally can display the on-chip temperature via JTAG. See *Figure 12*