Compact Zynq System 2017.1 with SW-defined Floating-Point 8xSIMD EdkDSP Accelerator

Description

This report describes design of compact HW system based on Zynq all programmable 28nm chip with two Arm A9 processors and programmable logic area. System is optimised for Ethernet connected computing nodes serving for industrial automation, local data processing and data communication. The documented HW architecture is one of candidates for wider use within the ECSEL Productive 4.0 project for the edge computing node in the Industry 4.0 solutions.

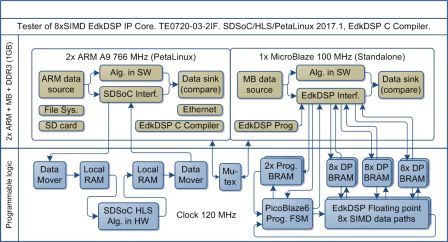

The demonstrated Zynq system includes the run-time reprogrammable 8xSIMD EdkDSP IP core. It combines the MicroBlaze and the floating point single Instruction multiple data (SIMD) data flow unit (DFU). The SIMD DFU is controlled by a run-time reprogrammable finite state machine implemented by Xilinx PicoBlaze6 8 bit controller with dedicated embedded (on Zynq executed) C compiler.

The application note describes the installation of the HW system, the SW API, algorithmic implementation and mapping to the 8xSIMD EdkDSP IP. Presented HW system is also compatible with the Xilinx SDSoC 2017.1 design environment. The SDSoC is supporting automated compilation of user-defined C/C++ ARM functions into HW accelerators with data movers (zero-copy, DMA, SG-DMA) and the automated integration of generated accelerators with the ARM Linux or stand-alone operating systems.

Package Summary

| Title | Compact Zynq System 2017.1 with SW-defined Floating-Point 8xSIMD EdkDSP Accelerator |

| Download | TE0720_MB_EdkDSP_1x8_zsys_2if_ila_8k_usb_te0706_sw1_INSTALL.zip productive40_t20i2m4_2017_1_te0706_02.pdf |

| License | productive40_t20i2m4_2017_1_te0706_02.pdf for licensing conditions. |

| Package content | ZIP archive with precompiled Vivado 2017.1 projects demonstrating Compact Zynq system 2017.1 on carrier TE0706-02 with SW-defined floating-point 8xSIMD EdkDSP accelerator. |

| Size | ZIP file: 323288586 Bytes PDF file: 4211470 Bytes |

| Required tools & platform |

Xilinx SDK 2017.1 |

| Installation notes | See productive40_t20i2m4_2017_1_te0706_02.pdf |

Result Category

| Project number | Year | RIV category | Comment |

| ECSEL 737459 | 2018 | Gfunk | Functional sample (demo) |